Блацкфин процесор је дизајниран, развијен и пласиран на тржиште преко Аналог Девицес & Интел као Мицро Сигнал Арцхитецтуре (МСА). Архитектура овог процесора је објављена у децембру 2000. године и први пут демонстрирана на ЕСЦ ( Уграђени системи Конференција) у јуну 2001. Овај Блацкфин процесор је углавном дизајниран да достигне ограничења снаге и рачунарске захтеве постојећих уграђених аудио, видео и комуникационих апликација. Овај чланак разматра преглед а Блацкфин процесор – архитектура и њене примене.

Шта је Блацкфин процесор?

Блацкфин процесор је 16 или 32-битни микропроцесор који укључује уграђену ДСП функционалност фиксне тачке која се испоручује преко 16-битних МАЦ-ова (множи–акумулира). Ове процесори су углавном дизајнирани за комбиновану процесорску архитектуру мале потрошње која може да покреће ОС док истовремено обавља тешке нумеричке задатке као што је Х.264 видео кодирање у реалном времену.

Овај процесор комбинује 32-битну РИСЦ и дуалну 16-битну МАЦ функционалност обраде сигнала тако што лако користи атрибуте који се налазе у микроконтролерима опште намене. Дакле, ова комбинација атрибута обраде омогућава Блацкфин процесорима да постигну слично добро и у контролној обради и у апликацијама за обраду сигнала. Ова способност у великој мери поједностављује и задатке имплементације хардверског и софтверског дизајна.

Блацкфин карактеристике:

- Овај процесор има архитектуру једног скупа инструкција, укључујући перформансе обраде које једноставно задовољавају/побеђују асортиман производа дигитални сигнални процесор или ДСП да обезбеди бољу цену, снагу и ефикасност меморије.

- Овај процесор са 16 или 32-битном архитектуром једноставно омогућава надолазеће уграђене апликације.

Обрада мултимедије, сигнала и контроле унутар једног језгра. - Повећава продуктивност програмера.

- Има подесиве перформансе кроз динамичко управљање напајањем за потрошњу енергије или обраду сигнала.

- Веома брзо се усваја у различите дизајне који су једноставно подржани од неколико ланаца алата као и оперативних система.

- Захтева минималну оптимизацију због развојног окружења моћног софтвера у комбинацији са перформансама језгра.

- Блацкфин процесор подржава водеће алате за развој у индустрији.

- Перформансе овог процесора и половина снаге конкурентских ДСП-а омогућавају напредне спецификације и нове апликације.

Архитектура Блацкфин процесора

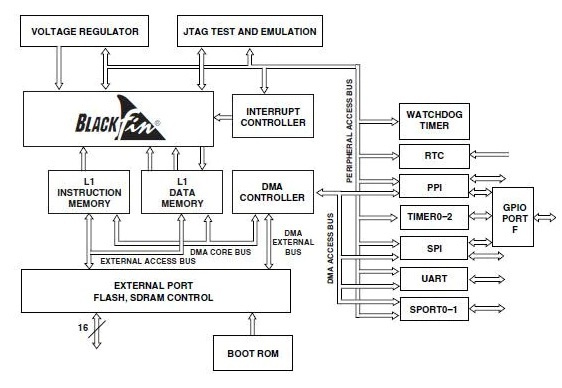

Блацкфин процесор пружа и функционалност микроконтролерске јединице и Дигитална обрада сигнала унутар једног процесора омогућавајући флексибилност. Дакле, овај процесор укључује СИМД (сингле иструцтион мултипле дата) процесор укључујући неке карактеристике као што је променљива дужина РИЗИК упутства, ватцхдог тајмер, ПЛЛ на чипу, јединица за управљање меморијом, сат реалног времена, серијски портови са 100 Мбпс, УАРТ контролори и СПИ луке.

ММУ подржава вишеструке ДМА канали за пренос података између периферних уређаја и ФЛАСХ, СДРАМ и СРАМ меморијских подсистема. Такође подржава кеш меморије података и конфигурабилне инструкције на чипу. Блацкфин процесор је једноставан хардвер који подржава 8, 16 и 32-битне аритметичке операције.

Блацкфин архитектура је углавном заснована на архитектури микро сигнала и њу су заједнички развили АДИ (Аналог Девицес) и Интел, која укључује 32-битни РИСЦ скуп инструкција и 8-битни сет видео инструкција са двоструким 16-битним множењем-акумулацијом (МАЦ) јединице.

Аналогни уређаји су способни да постигну равнотежу између ДСП и МЦУ захтева кроз архитектуру скупа инструкција компаније Блацкфин. Генерално, Блацкфин процесор је повезан са моћним алатима за развој софтвера ВисуалДСП++, али сада коришћењем Ц или Ц++, могуће је произвести високо ефикасан код веома лако него раније. За захтеве у реалном времену, подршка оперативног система постаје критична, тако да Блацкфин подржава не. оперативних система и заштите меморије. Блацкфин процесор долази у једнојезгарним моделима као што су БФ533, БФ535 и БФ537, као иу моделима са два језгра као што је БФ561.

Архитектура Блацкфин процесора укључује различите периферне уређаје на чипу као што су ППИ (паралелни периферни интерфејс), СПОРТС (серијски портови), СПИ (серијски периферни интерфејс), УАРТ (универзални асинхрони пријемни предајник), тајмери опште намене, РТЦ (у реалном времену). Сат), Ватцхдог тајмер, У/И опште намене (програмабилне заставице), Интерфејс мреже контролера (ЦАН). , мрежни МАЦ, периферни ДМА -12, ДМА меморије у меморију -2 укључујући Хандсхаке ДМА, ТВИ (двожични интерфејс) контролер, дебуг или ЈТАГ Интерфејс и руковалац догађаја са 32 Прекидати Инпутс. Све ове периферне јединице у архитектури су једноставно повезане преко различитих магистрала високог пропусног опсега са језгром. Дакле, опис неких од ових периферних уређаја је дат у наставку.

ППИ или паралелни периферни интерфејс

Блацкфин процесор једноставно обезбеђује ППИ који је такође познат као паралелни периферни интерфејс. Овај интерфејс је директно повезан са паралелним аналогно-дигиталним и дигитално-аналогним претварачима, видео кодерима и декодерима, као и са другим периферним уређајима опште намене.

Овај интерфејс укључује наменски улазни ЦЛК пин, три пина за синхронизацију оквира и 16 пинова за податке. Овде, улазни ЦЛК пин једноставно подржава паралелне брзине података једнаке половини ЦЛК брзине система. Три различита ИТУ-Р 656 режима подржавају само активни видео, вертикално затамњење и комплетно поље.

ППИ-јеви режими опште намене су дати да одговарају различитим апликацијама за пренос и хватање података. Дакле, ови режими су раздвојени у главне категорије Пријем података кроз интерно генерисану синхронизацију оквира, пренос података кроз интерно генерисану синхронизацију оквира, пренос података кроз екстерно генерисану синхронизацију оквира и податке примљене преко екстерно генерисаних синхронизација оквира.

СПОРТ

Блацкфин процесор укључује два двоканална синхрона серијска порта СПОРТ0 и СПОРТ1 који се користе за серијску и вишепроцесонску комуникацију. Дакле, ово су брзи и синхрони серијски портови који подржавају И²С , ТДМ и разни други конфигурабилни режими кадрирања за повезивање ДАЦс , АДЦ, ФПГАс и други процесори.

СПИ или порт за серијски периферни интерфејс

Блацкфин процесор укључује СПИ порт који омогућава процесору да разговара са различитим СПИ компатибилним уређајима. Овај интерфејс једноставно користи три пина за пренос података, пинове података-2 и један ЦЛК пин. Одабрани улазни и излазни пинови СПИ порта једноставно дају пуни дуплекс ССИ (синхрони серијски интерфејс) који подржава и мастер и славе режим, као и мулти-мастер окружења. Брзина преноса овог СПИ порта и фаза или поларитети такта се могу програмирати. Овај порт има уграђен ДМА контролер који подржава било пренос/пријем токова података.

Тајмери

Блацкфин процесор има 9 програмабилних тајмер јединица. Ови тајмери генеришу прекиде у језгру процесора за обезбеђивање периодичних догађаја намењених за синхронизацију са тактом процесора или са бројем спољних сигнала.

УАРТ

Термин УАРТ означава порт за „универзални асинхрони пријемник предајник“. Блацкфин процесор обезбеђује 2-полу-дуплекс УАРТ порта, који су у потпуности прилагођени стандардним ПЦ УАРТ-овима. Ови портови једноставно обезбеђују основни УАРТ интерфејс за друге хостове или периферне уређаје како би обезбедили полудуплексни, асинхрони серијски пренос података који подржава ДМА.

УАРТ портови укључују 5 до 8 битова података и 1 или 2 стоп бита и подржавају 2 начина рада као што су Програмирани И/О & ДМА. У првом режиму, процесор преноси или прима податке кроз читање/уписивање И/О мапираних регистара, где год се подаци двапут баферују и за пренос и за пријем. У другом режиму, ДМА контролер преноси и прима податке и смањује број прекида неопходних за пренос података из и у меморију.

РТЦ или сат реалног времена

Сат реалног времена Блацкфин процесора једноставно пружа различите функције као што су штоперица, тренутно време и аларм. Дакле, сат реалног времена ради са кристалом од 32,768 кХз који је екстерни у односу на Блацкфин процесор. РТЦ унутар процесора има пинове за напајање, који могу остати укључени и тактирани чак и када је остатак Блацкфин процесора у стању ниске потрошње. Сат реалног времена пружа низ програмабилних опција прекида. Улазна ЦЛК фреквенција од 32,768 кХз је раздвојена на сигнал од 1 Хз преко предскалера. Слично другим уређајима, сат реалног времена може да пробуди Блацкфин процесор из режима дубоког спавања/ режима мировања.

Ватцхдог Тимер

Блацкфин процесор има 32-битни ватцхдог тајмер, који се користи за извршавање софтверске функције надзора. Дакле, програматор иницијализује вредност бројача тајмера која омогућава исправан прекид, а затим дозвољава тајмер. Након тога, софтвер мора поново учитати бројач пре него што броји од програмиране вредности до „0“.

ГПИО или У/И опште намене

ГПИО је дигитални сигнални пин који се користи као улаз, излаз или обоје и контролише се преко софтвера. Блацкфин процесор укључује ГПИО (генерал-пурпосе И/О) пинове, 48-би-дирецтионал преко 3 одвојена ГПИО модула као што су ПОРТФИО, ПОРТХИО и ПОРТГИО повезани са портом Г, портом Х и портом Ф. Сваки пин порта опште намене се контролише појединачно кроз манипулацију статусом, контролом порта и регистрима прекида као што су ГПИО ДЦР, ГПИО ЦСР, ГПИО ИМР и ГПИО ИСР.

Етхернет МАЦ

Етхернет МАЦ периферија у Блацкфин процесору обезбеђује 10 до 100 Мб/с између МИИ (Медиа Индепендент Интерфаце) и периферног подсистема Блацкфина. МАЦ једноставно ради у Фулл-Дуплек и Халф-Дуплек режимима. Контролер приступа медијима је интерно тактиран са ЦЛКИН пина процесора.

Меморија

Меморија архитектуре Блацкфин процесора једноставно обезбеђује блокове меморије нивоа 1 и нивоа 2 у имплементацији уређаја. Меморија Л1 попут меморије података и инструкција једноставно је директно повезана са језгром процесора, ради на комплетној системској ЦЛК брзини и пружа максималне перформансе система за сегменте алгоритма критичног времена. Л2 меморија попут СРАМ меморије је већа и пружа мало смањене перформансе, али је и даље бржа у поређењу са меморијом ван чипа.

Структура Л1 меморије је имплементирана да обезбеди перформансе потребне за обраду сигнала док нуди програме у микроконтролерима. Ово се постиже једноставним дозвољавањем меморији Л1 да буде уређена као СРАМ, кеш меморија, иначе комбинација оба.

Подржавајући моделе кеша и СРАМ програмирања, дизајнери система додељују критичне скупове података за обраду сигнала у реалном времену којима је потребна ниска латенција и велики пропусни опсег у СРАМ, док чувају контролу у реалном времену или задатке ОС у кеш меморији.

Режими покретања

Блацкфин процесор укључује шест механизама за аутоматско учитавање интерне Л1 меморије инструкција након ресетовања. Дакле, различити режими покретања углавном укључују; Режим покретања са 8-битне & 16-битне вањске флеш меморије, серијске СПИ меморије. СПИ хост уређај, УАРТ, серијска ТВИ меморија, ТВИ Хост и обављају се из 16-битне екстерне меморије, заобилазећи серију покретања. За сваки од првих 6 режима покретања, прво се чита 10-бајтно заглавље са спољашњег меморијског уређаја. Дакле, заглавље означава бр. бајтова који ће се пренети и адреса одредишта меморије. Неколико меморијских блокова може се учитати кроз било коју серију покретања. Када се сви блокови једноставно учитају, онда извршавање програма почиње од почетка Л1 инструкције СРАМ.

Режими адресирања

Режими адресирања блацкфин процесора једноставно одређују како ће појединачна приступна меморија и адресирање одредити локацију. Режими адресирања који се користе у блацкфин процесору су индиректно адресирање, аутоинкремент/декремент, пост модификовање, индексирано са тренутним померањем, кружни бафер и бит реверс.

Индиректно адресирање

У овом режиму, поље адресе унутар инструкције укључује локацију меморије или регистра где год је присутна адреса ефикасног операнда. Ово адресирање је класификовано у две категорије као што су Индиректно регистровање и Индиректно памћење.

На пример ЛОАД Р1, @300

У горњој инструкцији, ефективна адреса се једноставно чува на меморијској локацији 300.

Аутоинкремент/Декремент Аддрессинг

Адресирање са аутоматским инкрементом једноставно ажурира Поинтер као и индексне регистре након права уласка. Количина прираста углавном зависи од величине речи. Приступ 32-битним речима може резултирати у ажурирању показивача са „4“. 16-битни приступ речи ажурира показивач са „2“, а 8-битни приступ речи ажурира показивач са „1“. Операције читања и 8-битног и 16-битног могу указивати на нулто проширење/проширивање предзнака садржаја у циљни регистар. Поинтер регистри се углавном користе за 8, 16 и 32-битне приступе, док се индексни регистри користе само за 16 и 32-битне приступе

На пример: Р0 = В [ П1++ ] (З) ;

У горњој инструкцији, 16-битна реч се учитава у 32-битни одредишни регистар са означене адресе преко регистра показивача „П1“. Након тога, показивач се повећава са 2 и реч је „0“ проширена да попуни 32-битни одредишни регистар.

Слично, аутоматско смањивање функционише тако што смањује адресу након права на улазак.

На пример: Р0 = [ И2– ] ;

У горњој инструкцији, 32-битна вредност се учитава у одредишни регистар и смањује индексни регистар за 4.

Адресирање након модификације

Овај тип адресирања једноставно користи вредност у регистрима индекса/показивача као што је ефикасна адреса. Након тога га модификује садржајем регистра. Индексни регистри се једноставно мењају са модификованим регистрима, док се регистри показивача мењају другим регистрима показивача. Као и одредишни регистри, адресирање типа после модификације не подржава регистре показивача.

На пример: Р3 = [ П1++П2 ] ;

У горњој инструкцији, 32-битна вредност се учитава у регистар „Р3“ и налази се на локацији меморије на коју указује регистар „П1“. Након тога, вредност у регистру „П2“ се додаје вредности у регистру П1.

Индексирано са тренутним померањем

Индексирано адресирање једноставно дозвољава програмима да добију вредности из табела података. Регистар показивача се мења непосредним пољем, након тога се користи као ефективна адреса. Дакле, вредност регистра показивача није ажурирана.

На пример, ако је П1 = 0к13, онда би [П1 + 0к11] ефикасно био еквивалент [0к24], који је повезан са свим приступима.

Бит Реверсе Аддрессинг

За неке алгоритме, програми захтевају адресирање преноса обрнутог бита да би добили резултате у секвенцијалном редоследу, посебно за прорачуне ФФТ (брза Фуријеова трансформација). Да би се задовољили захтеви ових алгоритма, функција адресирања обрнутих битова у Генераторима адреса података више пута дозвољава поделу серије података и чување ових података у обрнутом редоследу битова.

Цирцулар Буффер Аддрессинг

Блацкфин процесор пружа функцију као што је опционо кружно адресирање које једноставно повећава индексни регистар за унапред дефинисани опсег адреса, након чега аутоматски ресетује индексне регистре да би поновио тај опсег. Дакле, ова функција побољшава перформансе улазно/излазне петље једноставним уклањањем индексног показивача адресе сваки пут.

Кружно адресирање бафера је веома корисно када се више пута учитава или чува низ блокова података фиксне величине. Садржај кружног пуфера мора да испуњава следеће услове:

- Максимална дужина кружног бафера треба да буде број без предзнака са магнитудом испод 231.

- Величина модификатора мора бити испод дужине кружног бафера.

- Прва локација показивача „И“ мора бити у кружном баферу који је дефинисан дужином „Л“ и базом „Б“.

Ако било који од горе наведених услова није задовољен, онда се не наводи понашање процесора.

Регистрирајте датотеку Блацкфин процесора

Блацкфин процесор укључује три дефинитивне регистарске датотеке као што су; Датотека регистра података, датотека регистра показивача и ДАГ регистар.

- Датотека регистра података прикупља операнде користећи магистрале података које се користе за рачунске јединице и чува резултате израчунавања.

- Датотека регистра показивача укључује показиваче који се користе за операције адресирања.

- ДАГ регистри управљају кружним баферима који се користе за ДСП операције.

Блацкфин процесор пружа првокласно управљање напајањем и перформансе. Они су дизајнирани са методологијом пројектовања ниског напона и мале снаге која је у стању да варира и напон и радну фреквенцију како би значајно смањила укупну искоришћеност енергије. Дакле, ово може довести до значајног смањења искоришћења енергије, у поређењу са само променом радне фреквенције. Дакле, ово једноставно омогућава дужи век батерије за згодне уређаје.

Блацкфин процесор подржава различите екстерне меморије као што су ДДР-СДРАМ, СДРАМ, НАНД флеш, СРАМ & НОР флеш. Неки Блацкфин процесори такође садрже интерфејсе за масовно складиштење података као што су СД/СДИО и АТАПИ. Такође могу да подрже 100 мегабајта меморије унутар простора спољне меморије.

Предности

Тхе предности Блацкфин процесора укључи следеће.

- Блацкфин процесори пружају основне предности дизајнеру система.

- Блацкфин процесор нуди софтверску флексибилност као и скалабилност за конвергентне апликације као што су аудио, видео, обрада гласа и слике у више формата, сигурност у реалном времену, контролна обрада и вишемодна обрада пакета основног опсега

- Ефикасан капацитет обраде контроле и обрада сигнала високих перформанси омогућавају различита нова тржишта и апликације.

- ДПМ (Динамиц Повер Манагемент) омогућава дизајнеру система да посебно модификује потрошњу енергије уређаја према захтевима крајњег система.

- Ови процесори значајно смањују време и трошкове развоја.

Апликације

Тхе апликације Блацкфин процесора укључи следеће.

- Блацкфин процесори су идеални за многе апликације као што су АДАС (аутомобилски напредни системи помоћи возачу) , системи за надзор или безбедност и вид индустријске машине.

- Блацкфин апликације укључују системе за контролу серво мотора, аутомобилску електронику, системе за праћење и мултимедијалне потрошачке уређаје.

- Ови процесори једноставно обављају функције микроконтролера и обраде сигнала.

- Користе се за аудио, контролу процеса, аутомобиле, тестирање, мерење итд.

- Блацкфин процесори се користе у апликацијама за обраду сигнала као што су широкопојасни бежични, мобилне комуникације и интернет уређаји који подржавају аудио или видео.

- Блацкфин се користи у конвергентним апликацијама као што су умрежени и стримовани медији, дигитална кућна забава, аутомобилска телематика, инфотаинмент, мобилна ТВ, дигитални радио итд.

- Блацкфин процесор је уграђени процесор који има енергетску ефикасност и највеће перформансе који се користе у апликацијама где су важни мулти-форматни глас, аудио, видео, мулти-моде басебанд, обрада слике, обрада пакета, безбедност и контрола у реалном времену.

Дакле, ово је преглед Блацкфин процесора – архитектура, предности и њене примене. Овај процесор обавља обраду сигнала и функције микроконтролера. Ево питања за вас, шта је процесор?