ЈТАГ (Јоинт Тест Ацтион Гроуп) је добро успостављен ИЕЕЕ 1149.1 стандард који је развијен 1980. године да би решио производне проблеме који су се појавили у електронским плочама или штампане плоче . Ова технологија се користи да обезбеди довољан приступ тесту за сваку сложену плочу када се приступ тесту смањује. Тако је лансирана технологија скенирања граница & ЈТАГ стандард или ЈТАГ спецификација је успостављена. Сложеност електронике расте из дана у дан, тако да је ЈТАГ спецификација постала прихваћени тестни формат за тестирање компликованих и компактних електронских јединица. Овај чланак разматра преглед а ЈТАГ протокол – рад са апликацијама.

Шта је ЈТАГ?

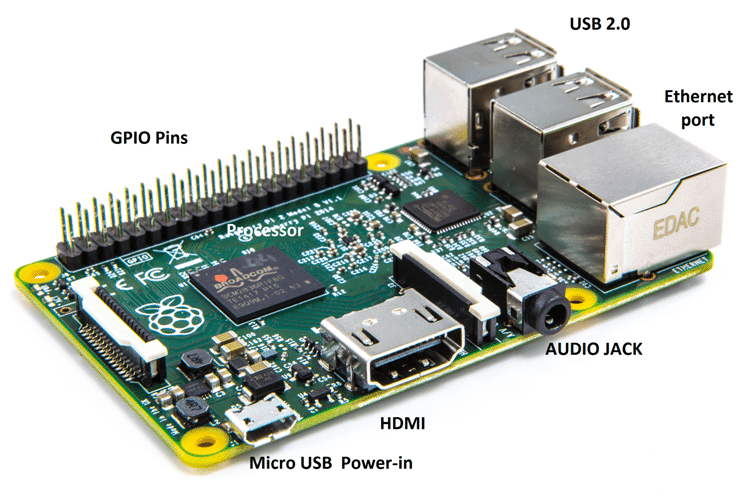

Име које је дато ИЕЕЕ 1149.1 стандардном тестном приступном порту, као и архитектури граничног скенирања, познато је као ЈТАГ (Јоинт Тест Ацтион Гроуп). Ова архитектура граничног скенирања се углавном користи унутар рачунара процесори јер је први процесор са ЈТАГ издао Интел. Овај ИЕЕЕ стандард једноставно дефинише како се кола рачунара тестирају да би се потврдило да ли исправно ради након процедуре производње. На штампаним плочама се врше испитивања за проверу лемних спојева.

Заједничка акциона група за тестирање обезбеђује пин-оут приказ за тестере са сваким ИЦ јастучићем који помаже у идентификацији било каквих грешака унутар плоче. Једном када се овај протокол повеже са чипом, ово може причврстити сонду на чип омогућавајући програмеру да контролише чип, као и његове везе са другим чиповима. Програмери такође могу да користе интерфејс са групом Јоинт Тест Ацтион за копирање фирмвера у непроменљиву меморију у електронском уређају.

Конфигурација/Пин Оут

Заједничка акциона група за тестирање укључује 20 пинова где су сваки пин и његова функција описани у наставку.

Пин1 (ВТреф): Ово је пин референтног напона циља који се користи за повезивање на главно напајање мете које се креће од 1,5 до 5,0 ВДЦ.

Пин2 (Внабавка): Ово је циљни напон напајања који се користи за повезивање главног напона циљаног 1.5ВДЦ – 5.0ВДЦ.

Пин3 (нТРСТ): Ово је тестни пин за ресетовање који се користи за ресетовање стања машине ТАП контролера.

Игле (4, 6, 8, 10, 12, 14, 16, 18 и 20): Ово су уобичајени ГНД пинови.

Пин5 (ТДИ): Ово су подаци о тесту у пину. Ови подаци се пребацују у циљни уређај. Ова игла мора бити извучена у дефинисаном стању на циљној плочи.

Пин7 (ТМС): Ово је пин стања тестног режима који се повлачи да би се одредило следеће стање машине стања ТАП контролера.

Пин9 (ТЦК): Ово је тестни пин такта који синхронизује операције унутрашње машине стања у ТАП контролеру.

Пин11 (РТЦК): Ово је улазни повратни ТЦК пин који се користи у уређајима који подржавају адаптивно тактирање.

Пин13 (ТДО): Ово је пин за излаз података за тестирање, тако да се подаци премештају из циљног уређаја у Флисваттер.

Пин15 (нСРСТ): Ово је пин за ресетовање циљаног система који је повезан са главним сигналом за ресетовање мете.

Пинови 17 и 19 (НЦ): Ово нису повезани пинови.

ЈТАГ Воркинг

Првобитна употреба ЈТАГ-а је за тестирање граница. Овде је једноставна штампана плоча која укључује две ИЦ-а као што су ЦПУ и ФПГА . Типична плоча може укључивати многе ИЦ-ове. Уопштено говорећи, ИЦ-ови укључују много пинова који су повезани заједно са многим везама. Овде, на следећем дијаграму, приказане су само четири везе.

Дакле, ако дизајнирате много плоча где свака плоча има хиљаде веза. У томе има лоших табли. Дакле, треба да проверимо која плоча ради, а која не ради. За то је осмишљена Заједничка акциона група за тестирање.

Овај протокол може да користи контролне пинове свих чипова, али на следећем дијаграму, Заједничка акциона група за тестирање ће направити све излазне пинове ЦПУ-а и све улазне пинове ФПГА. Након тога, преношењем одређене количине података са пинова ЦПУ-а и читањем вредности пинова са ФПГА, ЈТАГ изјављује да су везе на ПЦБ плочи у реду.

Заправо, Заједничка акциона група за тестирање укључује четири логичка сигнала ТДИ, ТДО, ТМС & ТЦК. И ови сигнали морају бити повезани на посебан начин. У почетку, ТМС & ТЦК су повезани паралелно са свим ИЦ-овима ЈТАГ-а.

Након тога, и ТДИ и ТДО су повезани за формирање ланца. Као што можете приметити, свака ЈТАГ компатибилна ИЦ укључује 4-пинова који се користе за ЈТАГ где су 3-пина улаз, а 4. пин је излаз. Пети пин као ТРСТ је опциони. Обично се ЈТАГ пинови не деле у друге сврхе.

Користећи Јоинт Тест Ацтион Гроуп, сви ИЦ-ови користе тестирање граница које је оригинални разлог креирао ЈТАГ. Тренутно је употреба овог протокола проширена како би се омогућиле различите ствари као што је конфигурисање ФПГА и након тога се ЈТАГ користи у ФПГА језгру за потребе отклањања грешака.

ЈТАГ Арцхитецтуре

ЈТАГ архитектура је приказана испод. У овој архитектури, сви сигнали између основне логике уређаја и пинова се прекидају кроз серијску путању скенирања која се зове БСР или гранични регистар скенирања. Овај БСР укључује различите 'ћелије' за скенирање граница. Генерално, ове граничне ћелије за скенирање нису видљиве, али се могу користити за постављање или читање вредности у тест режиму са пинова уређаја.

ЈТАГ интерфејс који се назива ТАП или тест приступни порт користи различите сигнале за подршку операције скенирања граница као што су ТЦК, ТМС, ТДИ, ТДО и ТРСТ.

- Сигнал ТЦК или тест часовника једноставно синхронизује унутрашње операције државног строја.

- ТМС или Тест Моде Селецт сигнал се узоркује на растућој ивици сигнала тест такта за одлучивање о следећем стању.

- ТДИ или Тест Дата Ин сигнал означава померене податке у уређај за тестирање, иначе логику програмирања. Када је унутрашња машина стања у правом стању, узоркује се на растућој ивици ТЦК.

- ТДО или излазни сигнал тестних података означава померене податке тестног уређаја, иначе логику програмирања. Када је унутрашња машина стања у правом стању, она важи на опадајућој ивици ТЦК

- ТРСТ или Тест Ресет је опциони пин који се користи за ресетовање машине стања ТАП контролера.

ТАП контролер

Тестна приступна тачка у архитектури ЈТАГ-а састоји се од ТАП контролера, регистра инструкција и регистара тестних података. Овај контролер укључује машину за тестирање која је одговорна за читање ТМС & ТЦК сигнала. Овде се и/п пин података једноставно користи за учитавање података у граничне ћелије између ИЦ језгра и физичких пинова, као и за учитавање података у један од регистара података или у регистар инструкција. Подаци о/п пин се користи за читање података било из регистара или граничних ћелија.

Државну машину ТАП контролера контролише ТМС и тактује ТЦК. Машина стања користи две путање за означавање два различита режима као што су режим инструкција и режим података.

Регистри

Постоје две врсте регистара доступних у оквиру скенирања граница. Сваки компатибилни уређај укључује најмање два или више регистра података и један регистар инструкција.

Регистар инструкција

Регистар инструкција се користи за чување тренутне инструкције. Дакле, ТАП контролер користи његове податке да одлучи шта да изврши са добијеним сигналима. Најчешће, подаци регистра инструкција ће описати коме од регистра података морају бити прослеђени сигнали.

Регистри података

Регистри података су доступни у три типа: БСР (Боундари Сцан Регистер), БИПАСС & ИД ЦОДЕС регистар. Такође, могу постојати и други регистри података, али они нису неопходни као елемент ЈТАГ стандарда.

Гранични регистар скенирања (БСР)

БСР је главни регистар података за тестирање који се користи за пребацивање података са и на И/О пинове уређаја.

ЗАОБИЋИ

Бипасс је једнобитни регистар који се користи за прослеђивање података из ТДИ – ТДО. Дакле, омогућава да се додатни уређаји унутар кола тестирају минималним трошковима.

ИД КОДОВИ

Овај тип регистра података укључује ИД код као и број ревизије за уређај. Дакле, ови подаци омогућавају да се уређај повеже са својом БСДЛ (Боундари Сцан Десцриптион Лангуаге) датотеком. Ова датотека је укључивала детаље конфигурације Боундари Сцан за уређај.

Рад ЈТАГ-а је, у почетку, изабран режим инструкција где једно од стања у овом режиму „путања“ дозвољава оператеру да тактује у оквиру инструкције од стране ТДИ. Након тога, државни строј се развија док се не преуреди. Следећи корак за већину упутстава је избор режима података. Дакле, у овом режиму, подаци се учитавају преко ТДИ за читање из ТДО. За ТДИ & ТДО, путеви података ће бити распоређени у складу са инструкцијама које су унете. Када се операција читања/писања заврши, машина стања се поново развија у стање ресетовања.

Разлика између ЈТАГ и УАРТ

Разлика између ЈТАГ и УАРТ укључује следеће.

| ЈТАГ |

УАРТ |

| Термин „ЈТАГ“ је скраћеница за Јоинт Тест Ацтион Гроуп. | Термин ' УАРТ ” означава универзални асинхрони пријемник/предајник. |

| То је синхрони интерфејс који користи уграђени хардвер за програмирање блица . | УАРТ је асинхрони интерфејс који користи боотлоадер који ради у меморији. |

| То је скуп тестних портова који се користе за отклањање грешака, али се такође могу користити за програмирање фирмвера (што се обично ради).

|

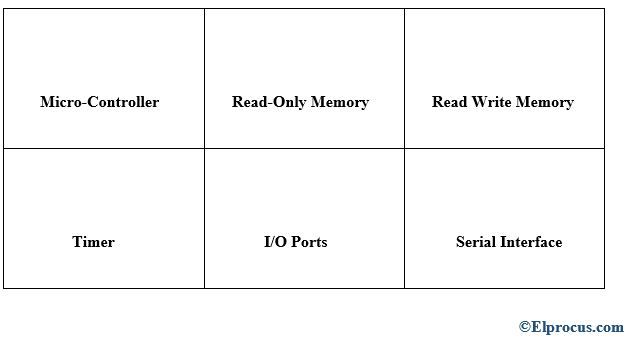

УАРТ је тип чипа који контролише комуникацију са и са уређаја, као што су микроконтролер, РОМ, РАМ, итд. Већину времена, то је серијска веза која нам омогућава да комуницирамо са уређајем. |

| Доступни су у четири типа ТДИ, ТДО, ТЦК, ТМС & ТРСТ. | Они су доступни у два типа глупог УАРТ-а и ФИФО УАРТ-а. |

| Јоинт Тест Ацтион Гроуп је протокол за серијско програмирање или приступ подацима који се користи у повезивању микроконтролера и сродних уређаја. | УАРТ је једна врста чипа иначе подкомпонента микроконтролера која се користи да обезбеди хардвер за генерисање асинхроног серијског тока као што је РС-232/РС-485. |

| ЈТАГ компоненте су процесори, ФПГА, ЦПЛДс , итд. | УАРТ компоненте су ЦЛК генератор, И/О регистри померања, бафери за пренос или пријем, бафер системске сабирнице података, контролна логика читања или писања итд. |

ЈТАГ анализатор протокола

ЈТАГ анализатор протокола као што је ПГИ-ЈТАГ-ЕКС-ПД је једна врста анализатора протокола укључујући неке функције за снимање и отклањање грешака у комуникацији између хоста и дизајна који се тестира. Овај тип анализатора је водећи инструмент који омогућава инжењерима за тестирање и дизајн да тестирају одређене дизајне ЈТАГ-а за његове спецификације кроз уређење ПГИ-ЈТАГ-ЕКС-ПД као што је Мастер или Славе за генерисање ЈТАГ саобраћаја и декодирање пакета за декодирање Протокол заједничке тест акционе групе.

Карактеристике

Карактеристике анализатора ЈТАГ протокола укључују следеће.

- Подржава до 25МХ ЈТАГ фреквенција.

- Истовремено генерише ЈТАГ саобраћај и декодирање протокола за сабирницу.

- Има ЈТАГ Мастер способност.

- Променљива ЈТАГ брзина података и радни циклус.

- Кориснички дефинисана ТДИ & ТЦК одлагања.

- Главни рачунар УСБ 2.0 или 3.0 интерфејс.

- Анализа грешака у оквиру декодирања протокола

- Временски дијаграм сабирнице декодиране протоколом.

- Непрекидан проток података протокола до главног рачунара за обезбеђивање великог бафера.

- Листа активности протокола.

- При различитим брзинама, скрипта за вежбање се може написати за комбиновање генерисања вишеструких оквира података.

Временски дијаграм

Тхе временски дијаграм ЈТАГ-а протокол је приказан испод. На следећем дијаграму, ТДО пин остаје у условима високе импедансе осим током стања схифт-ИР/ схифт-ДР контролера.

У условима схифт-ИР & Схифт-ДР контролера, ТДО пин се ажурира на опадајућој ивици ТЦК кроз Таргет и узоркује на растућој ивици ТЦК кроз Хост.

И ТДИ и ТМС пинови се једноставно узоркују на растућој ивици ТЦК кроз Таргет. Ажурирано на опадајућој ивици иначе ТЦК преко Хост-а.

Апликације

Тхе ЈТАГ апликације укључи следеће.

- Јоинт Тест Ацтион Гроуп се често користи у процесорима за обезбеђивање права уласка у њихове функције емулације или отклањања грешака.

- Сви ЦПЛД и ФПГА користе ово као интерфејс за приступ својим програмским функцијама.

- Користи се за тестирање ПЦБ-а без физичког приступа

- Користи се за тестове производње на нивоу плоче.

Дакле, ради се о томе преглед ЈТАГ-а – конфигурација пинова, рад са апликацијама. Индустријски стандард ЈТАГ се користи за верификацију дизајна, као и ПЦБ тестирање након производње. Ево питања за вас, ЈТАГ означава?