МОС транзистор је најосновнији елемент у дизајну интегрисаних кола великих размера. Ови транзистори су генерално класификовани у два типа ПМОС и НМОС. Комбинација НМОС и ПМОС транзистора је позната као а ЦМОС транзистор . Различити логичке капије и други дигитални логички уређаји који су имплементирани морају имати ПМОС логику. Ова технологија је јефтина и има добру отпорност на сметње. Овај чланак говори о једној од врста МОС транзистора као што је ПМОС транзистор.

Шта је ПМОС транзистор?

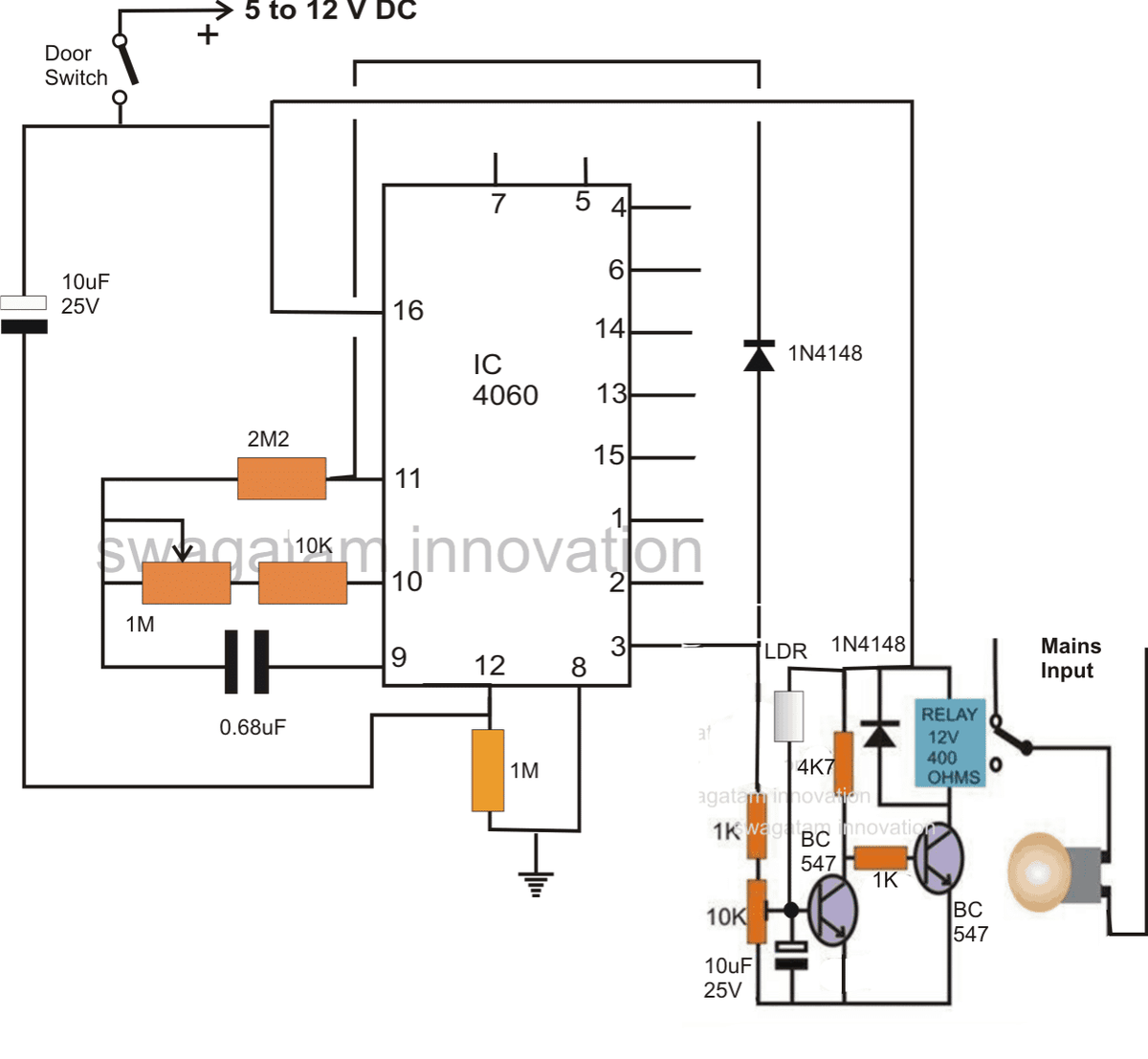

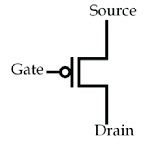

ПМОС транзистор или П-канални метални оксид полупроводник је врста транзистора где се додаци п-типа користе у региону канала или капије. Овај транзистор је управо обрнут од НМОС транзистора. Ови транзистори имају три главна терминала; извор, капија и одвод где је извор транзистора дизајниран са супстратом п-типа, а терминал за одвод је дизајниран са супстратом типа н. У овом транзистору, носиоци набоја попут рупа су одговорни за провођење струје. Симболи ПМОС транзистора су приказани испод.

Како ради ПМОС транзистор?

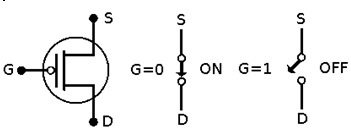

Рад транзистора п-типа је сасвим супротан од транзистора н-типа. Овај транзистор ће формирати отворено коло кад год добије напон који није занемарљив, што значи да нема протока електричне енергије од терминала капије (Г) до извора (С). Слично томе, овај транзистор формира затворено коло када добије напон од око 0 волти, што значи да струја тече од терминала капије (Г) до одвода (Д).

Овај мехур је такође познат као инверзиони мехур. Дакле, главна функција овог круга је да инвертује вредност улазног напона. Ако терминал капије обезбеђује напон од 1, онда ће га овај претварач променити у нулу и у складу са тим функционише коло. Дакле, функција ПМОС транзистора и НМОС транзистора је сасвим супротна. Једном када их спојимо у једно МОС коло, онда ће то постати ЦМОС (комплементарни метал-оксидни полупроводник) коло.

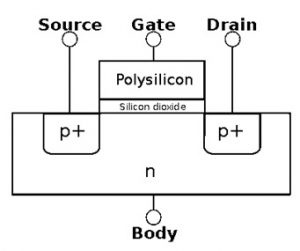

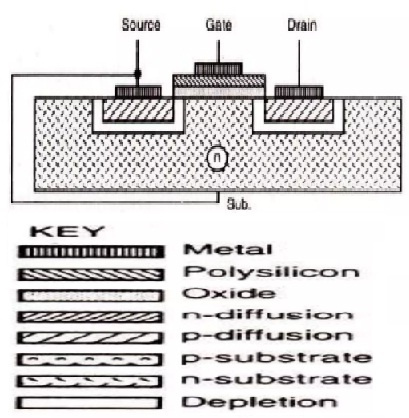

Попречни пресек ПМОС транзистора

Попречни пресек ПМОС транзистора је приказан испод. ПМОС транзистор је изграђен са телом н-типа укључујући два полупроводничка региона п-типа који су суседни капији. Овај транзистор има контролну капију као што је приказано на дијаграму која контролише проток електрона између два терминала као што су извор и одвод. У пМОС транзистору, тело се држи на +ве напону. Једном када је терминал гејта позитиван, тада су терминали извора и одвода обрнуто пристрасни. Када се то деси, нема протока струје, па ће се транзистор искључити.

Када се напон на терминалу гејта смањи, носиоци позитивног набоја ће бити привучени на дно интерфејса Си-СиО2. Кад год напон постане довољно низак, канал ће бити обрнут и створиће проводни пут од терминала извора до одвода дозвољавајући проток струје.

Кад год се ови транзистори баве дигиталном логиком, обично постоје две различите вредности као што су 1 и 0 (ОН и ОФФ). Позитивни напон транзистора је познат као ВДД који представља логичку високу (1) вредност унутар дигиталних кола. Нивои напона ВДД у ТТЛ логика били су углавном око 5В. Тренутно транзистори не могу да издрже тако високе напоне јер се обично крећу од 1,5В – 3,3В. Ниски напон је често познат као ГНД или ВСС. Дакле, ВСС означава логичку '0' и такође је нормално подешен на 0В.

ПМОС транзисторско коло

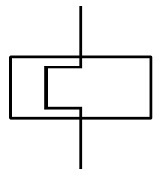

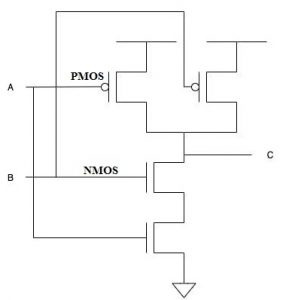

Дизајн НАНД капије користећи ПМОС транзистор и НМОС транзистор је приказан испод. Генерално, НАНД капија у дигиталној електроници је логичка капија која се такође назива НЕ-И капија. Излаз овог гејта је низак (0) само ако су два улаза висока (1) и његов излаз је допуна АНД капији. Ако је било који од два улаза ЛОВ (0), онда даје високе излазне резултате.

У доњем логичком колу, ако је улаз А 0, а Б 0, онда ће А улаз пМОС-а произвести „1“, а улаз нМОС-а ће произвести „0“. Дакле, ова логичка капија генерише логичку '1' јер је повезана са извором затвореним колом и одвојена од ГНД-а кроз отворено коло.

Када је А „0“, а Б“ је „1“, тада ће А улаз пМОС-а генерисати „1“, а А улаз НМОС-а ће генерисати „0“. Дакле, ова капија ће произвести логичку јер је повезана са извором кроз затворено коло и одвојена од ГНД-а отвореним колом. Када је А '1' и Б '0', тада ће 'Б' улаз пМОС-а генерисати висок излаз (1) и 'Б' улаз НМОС-а ће генерисати излаз као ниски (0). Дакле, ова логичка капија ће генерисати логичку 1 јер је повезана са извором кроз затворено коло и одвојена од ГНД-а преко отвореног кола.

Када је А '1' и Б '1', тада ће А улаз од 'пМОС' произвести нулу, а улаз нМОС ће генерисати '1'. Сходно томе, требало би да проверимо и Б улаз за пМОС и нМОС. Б улаз пМОС-а ће генерисати „0“, а Б улаз нМОС-а ће генерисати „1“. Дакле, ова логичка капија ће генерисати логичку '0' јер је одвојена од извора отвореним колом и повезана је са ГНД кроз затворено коло.

Табела истине

Табела истинитости горњег логичког кола је дата у наставку.

|

А |

Б |

Ц |

|

0 |

0 | 1 |

|

0 |

1 | 1 |

| 1 | 0 |

1 |

| 1 | 1 |

0 |

Гранични напон ПМОС транзистора је обично „Вгс“ који је неопходан за стварање канала познатог као инверзија канала. У ПМОС транзистору, супстрат и терминали извора су једноставно повезани на 'Вдд'. Ако почнемо да смањујемо напон позивајући се на терминал извора на терминалу гејта од Вдд до тачке где год приметите инверзију канала, на овој позицији ако анализирате да су Вгс и извор на високом потенцијалу, онда ћете добити негативну вредност. Дакле, ПМОС транзистор има негативну Втх вредност.

Процес израде ПМОС-а

Кораци укључени у производњу ПМОС транзистора су размотрени у наставку.

Корак 1:

Танак слој силицијумске плочице се мења у материјал Н-типа једноставним допирањем фосфорног материјала.

Корак 2:

Дебели слој силицијум диоксида (Сио2) се узгаја на комплетној подлози п-типа.

Корак 3:

Сада је површина премазана фоторезистом преко дебелог слоја силицијум диоксида.

Корак 4:

Након тога, овај слој се једноставно излаже УВ светлу кроз маску која дефинише оне регионе у које ће се одвијати дифузија заједно са транзисторским каналима.

Корак 5:

Ови региони су међусобно урезани са основним силицијум диоксидом тако да је површина плочице изложена унутар прозора дефинисаног маском.

Корак 6:

Преостали фоторезист се одваја и танак слој Сио2 обично расте на 0,1 микрометар преко целе површине чипа. Након тога, полисилицијум се поставља преко овога да би се формирала структура капије. Фоторезист се поставља преко целог слоја полисилицијума и излаже УВ светлу кроз маску2.

Корак 7:

Дифузије се постижу загревањем плочице до максималне температуре и пропуштањем гаса са жељеним нечистоћама п-типа као што је бор.

Корак 8:

Узгаја се силицијум диоксид дебљине 1 микрометар и на њега се наноси фотоотпорни материјал. Изложите ултраљубичастом светлу са маском3 на жељене делове капије, извора и одвода који су урезани да би се направили контактни резови.

Корак 9:

Сада се метал или алуминијум наноси на његову површину дебљине 1 микрометар. Поново се фотоотпорни материјал узгаја по целом металу и излаже УВ светлу кроз маску4 која је урезана да би се формирао потребан дизајн међуповезивања. Коначна ПМОС структура је приказана испод.

Карактеристике ПМОС транзистора

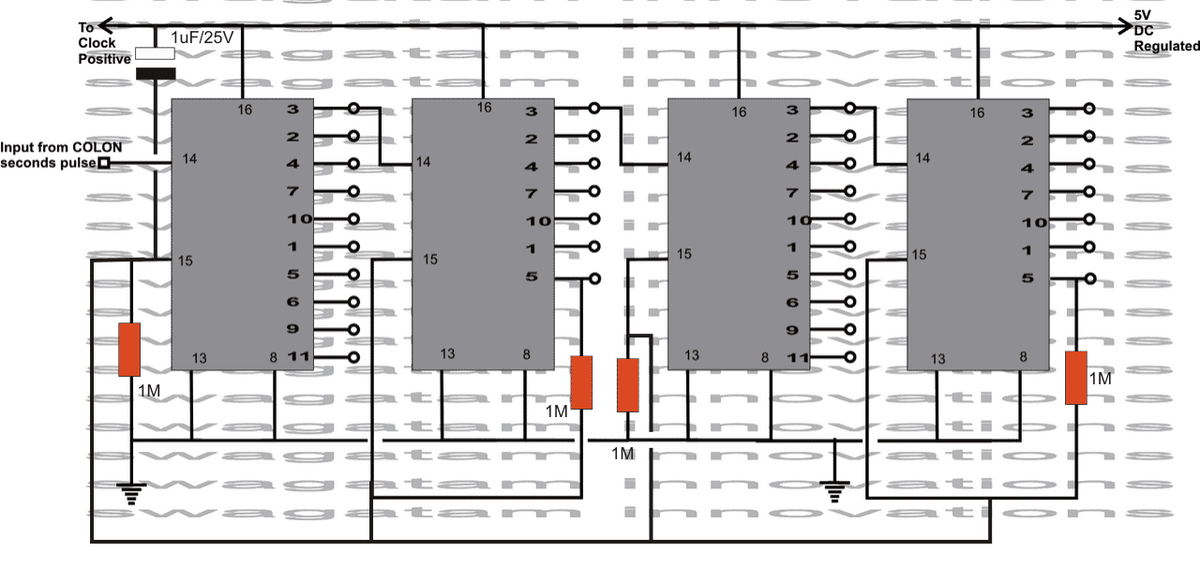

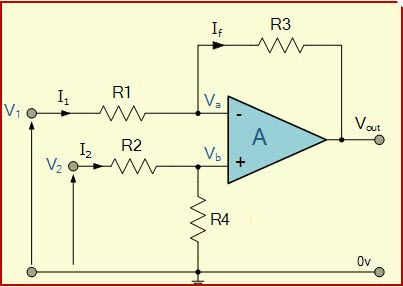

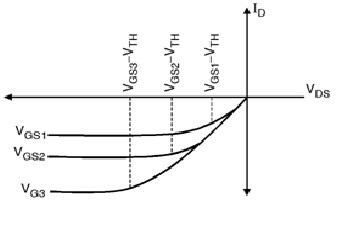

И-В карактеристике ПМОС транзистора су приказане испод. Ове карактеристике су подељене у два региона да би се добио однос између струје одвода и извора (И ДС) као и њених терминалних напона као што су линеарни и региони засићења.

У линијском региону, ИДС ће се линеарно повећати када се ВДС (одвод на извор напон) повећа, док је у региону засићења И ДС стабилан и независан је од ВДС. Главни однос између ИСД-а (од извора до одводне струје) и његових терминалних напона се изводи сличном процедуром НМОС транзистора. У овом случају, једина промена ће бити да су носиоци наелектрисања присутни унутар инверзионог слоја једноставно рупе. Када се рупе померају од извора до одвода, ток струје је такође исти.

Дакле, негативни предзнак се појављује унутар тренутне једначине. Поред тога, све примењене предрасуде на терминалима уређаја су негативне. Дакле, карактеристике ИД-а ПМОС транзистора - ВДС су приказане у наставку.

Једначина струје одвода за ПМОС транзистор у линеарном региону је дата као:

ИД = – мп Цок

Слично, једначина одводне струје за ПМОС транзистор у региону засићења је дата као:

ИД = – мп Цок (ВСГ – | В ТХ |п )^2

Где је 'мп' покретљивост рупе и '|ВТХ| п' је напон прага ПМОС транзистора.

У горњој једначини, негативни предзнак ће указивати да је ИД( струја одвода ) тече од одвода (Д) до извора (С), док рупе теку у супротном смеру. Када је покретљивост рупе ниска у поређењу са мобилношћу електрона, онда ПМОС транзистори пате од способности погона ниске струје.

Дакле, ово је све о прегледу ПМОС транзистора или мос транзистора п-типа – производње, кола и његовог рада. ПМОС транзистори су пројектовани са п-извором, н-супстратом и одводом. Носиоци набоја ПМОС-а су рупе. Овај транзистор води када се на терминалу капије примени низак напон. Уређаји засновани на ПМОС-у су мање склони сметњама у поређењу са НМОС уређајима. Ови транзистори се могу користити као отпорници контролисани напоном, активна оптерећења, струјна огледала, трансимпедансни појачивачи, а такође се користе у прекидачима и појачивачима напона. Ево питања за вас, шта је НМОС транзистор?