У дигитална електроника додавање двобитних бинарних бројева може бити могуће коришћењем полусабирач . А ако улазна секвенца има тробитну секвенцу, тада се поступак додавања може завршити коришћењем пуног сабирача. Али ако је број битова већи у улазној секвенци, тада се поступак може довршити употребом полусабирача. Будући да пуни сабирач не може да доврши операцију сабирања. Дакле, ови недостаци се могу превазићи употребом „Риппле Царри Аддер“. То је јединствена врста логичко коло користи се за додавање Н-битних бројева у дигиталним операцијама. Овај чланак описује преглед шта је риппле-царри-аддер и његов рад.

Шта је Риппле Царри Аддер?

Структура више пуних сабирача каскадира се на начин дајући резултате сабирања н бита бинарног низа. Овај сабирач укључује каскадне пуне сабираче у својој структури, тако да ће се ношење генерисати у свакој фази пуног сабирача у кругу са таласањем и сабирањем. Ови излази за пренос у свакој фази пуног сабирача прослеђују се свом следећем потпуном сабирачу и примењују се као уноси за пренос на њега. Овај процес се наставља до своје последње фазе потпуног сабирања. Дакле, сваки излазни бит ношења се таласа до следеће фазе пуног сабирача. Из тог разлога је назван „РИППЛЕ ЦАРРИ АДДЕР“. Најважнија његова карактеристика је додавање секвенци улазних битова било да је секвенца 4-битна или 5-битна или било која друга.

„Једна од најважнијих тачака коју треба размотрити у овом сабиру за пренос је коначни излаз познат тек након што се излази за ношење генеришу у свакој фази пуног сабирача и проследе у следећу фазу. Тако да ће доћи до кашњења како би се добио резултат помоћу овог сабирача за ношење ”.

Постоје разни типови додавача са таласима. Су:

- 4-битни таласасти сабирач

- 8-битни таласни носач

- 16-битни таласасти сабирач

Прво ћемо започети са 4-битним сабиром за ношење таласа, а затим са 8-битним и 16-битним збрајањем са таласима.

4-битни Риппле Царри Аддер

Дијаграм у наставку представља 4-битни збрајајући таласаст носач. У овом сабирачу, четири пуна збрајања су повезана каскадно. Цо је носиви улазни бит и увек је нула. Када се овај улазни пренос ‘Цо’ примени на две улазне секвенце А1 А2 А3 А4 и Б1 Б2 Б3 Б4, онда је излаз представљен са С1 С2 С3 С4, а излазни пренос Ц4.

4-битни РЦА дијаграм

Рад 4-битног Риппле Царри Аддера

- Узмимо пример две улазне секвенце 0101 и 1010. Они представљају А4 А3 А2 А1 и Б4 Б3 Б2 Б1.

- Према овом концепту сабирача, унос носи 0.

- Када се Ао & Бо примењују на 1. пуни сабирач заједно са улазним преносом 0.

- Овде је А1 = 1 Б1 = 0 Цин = 0

- Збир (С1) и пренос (Ц1) генерисаће се према једначинама Збир и Пренос овог сабирача. Према његовој теорији, излазна једначина за Сум = А1⊕Б1⊕Цин и Царри = А1Б1⊕Б1Цин⊕ЦинА1

- Према овој једначини, за 1. пуни сабирач С1 = 1 и Царри излаз, тј. Ц1 = 0.

- Исто као и за следеће улазне битове А2 и Б2, излаз С2 = 1 и Ц2 = 0. Овде је важна тачка да пуни сабирач другог степена добија улазни пренос, тј. Ц1 који је излазни пренос пуног сабирача почетне фазе.

- Овако ће добити коначни излазни низ (С4 С3 С2 С1) = (1 1 1 1) и излазни пренос Ц4 = 0

- Ово је поступак додавања за 4-битне секвенце уноса када се примењује на овај сабирач за пренос.

8-битни Риппле Царри Аддер

- Састоји се од 8 пуних сабирача који су повезани у каскадном облику.

- Сваки излаз ношења пуног сабирача повезан је као улазни пренос на пуни сабирач следеће фазе.

- Улазне секвенце су означене са (А1 А2 А3 А4 А5 А6 А7 А8) и (Б1 Б2 Б3 Б4 Б5 Б6 Б7 Б8), а његова релевантна излазна секвенца означена је са (С1 С2 С3 С4 С5 С6 С7 С8).

- Процес сабирања у 8-битном риппле-царри-аддер-у је исти принцип који се користи у 4-битном риппле-царри-аддер-у, тј. Сваки бит из две улазне секвенце додаће се заједно са улазним ношењем.

- Ово ће се користити када се додају две 8-битне бинарне секвенце.

8бит-таласни-носач-сабирач

16-битни Риппле Царри Аддер

- Састоји се од 16 пуних сабирача који су повезани у каскадном облику.

- Сваки излаз ношења пуног сабирача повезан је као улазни пренос на пуни сабирач следеће фазе.

- Улазне секвенце означене су са (А1 ... .. А16) и (Б1 ...... Б16), а његова релевантна излазна секвенца означена је са (С1 …… .. С16).

- Процес додавања у 16-битном риппле-царри-аддер-у је исти принцип који се користи у 4-битном риппле-царри-аддер-у, тј. Сваки бит из две улазне секвенце ће се додати заједно са улазним ношењем.

- Ово ће се користити када се додају две 16-битне бинарне цифре.

16-битни додатак за таласавање

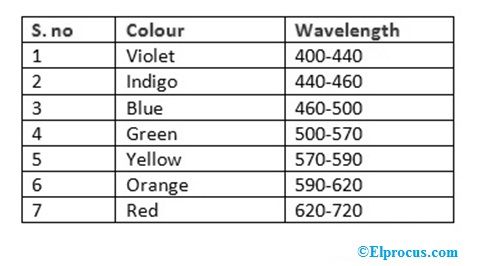

Табела истине Риппле Царри Аддер

Испод табеле истинитости приказане су излазне вредности за могуће комбинације свих улаза за таласање-ношење-сабирање.

| А1 | А2 | А3 | А4 | Б4 | Б3 | Б2 | Б1 | С4 | С3 | С2 | С1 | Носи |

0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 |

Риппле Царри Аддер ВХДЛ код

ВХДЛ (ВХСИЦ ХДЛ) је језик за опис хардвера. То је језик дигиталног дизајна. ВХДЛ код за овај сабирач је приказан испод.

библиотека ИЕЕЕ

користите ИЕЕЕ.СТД_ЛОГИЦ_1164.АЛЛ

ентитет Рипплецарриаддер је

Порт (А: у СТД_ЛОГИЦ_ВЕЦТОР (3 до 0)

Б: у СТД_ЛОГИЦ_ВЕЦТОР (3 до 0)

Цин: у СТД_ЛОГИЦ

С: излази СТД_ЛОГИЦ_ВЕЦТОР (3 до 0)

Цоут: оут СТД_ЛОГИЦ)

крај Рипплецарриаддер

архитектура Понашање Рипплецарриаддер-а је - Декларација о компонентама ВХДЛ кода пуног збрајања

компонента фулл_аддер_вхдл_цоде

Порт (А: у СТД_ЛОГИЦ

Б: у СТД_ЛОГИЦ

Цин: у СТД_ЛОГИЦ

С: излази СТД_ЛОГИЦ

Цоут: оут СТД_ЛОГИЦ)

крајња компонента

- Изјава о средњем ношењу

Сигнал ц1, ц2, ц3: СТД_ЛОГИЦ

започети

- Порт Маппинг Порт Фулл Аддер 4 пута

ФА1: мапа порта фулл_аддер_вхдл_цоде (А (0), Б (0), Цин, С (0), ц1)

ФА2: мапа порта фулл_аддер_вхдл_цоде (А (1), Б (1), ц1, С (1), ц2)

ФА3: мапа порта фулл_аддер_вхдл_цоде (А (2), Б (2), ц2, С (2), ц3)

ФА4: мапа порта фулл_аддер_вхдл_цоде (А (3), Б (3), ц3, С (3), Цоут)

крај Понашање

Верилог код Риппле Царри Аддер

Верилог код је језик за опис хардвера. Користи се у дигиталним круговима у фази РТЛ-а за пројектовање и верификацију. Верилог код за овај сабирач за ношење приказан је испод.

модул риппле_царри_аддер (а, б, цин, сум, цоут)

улаз [03: 0] а

улаз [03: 0] б

улаз цин

излаз [03: 0] сума

оутпут цоут

жица [2: 0] в

фулладд а1 (а [0], б [0], цин, збир [0], ц [0])

фулладд а2 (а [1], б [1], ц [0], збир [1], ц [1])

фулладд а3 (а [2], б [2], ц [1], збир [2], ц [2])

фулладд а4 (а [3], б [3], ц [2], збир [3], цоут)

ендмодуле

фулладд модул (а, б, ЦИН, сум, цоут)

улаз а, б, цин

излазна сума, прим

доделити суму = (а ^ б ^ цин)

доделити цоут = ((а & б) | (б & цин) | (а & цин))

Риппле Царри Аддер апликације

Апликације за додавање таласастог носача укључују следеће.

- Ови сабирници за ношење користе се углавном као додатак н-битним улазним секвенцама.

- Ови носачи су применљиви у дигиталној обради сигнала и микропроцесори .

Риппле Царри Аддер Предности

Предности додавања таласастог носача укључују следеће.

- Овај додатак за ношење има предност јер можемо да извршимо поступак додавања за н-битне секвенце да бисмо добили тачне резултате.

- Дизајнирање овог сабирача није сложен процес.

Таласни носач носача је алтернатива када пола сабирача и пуни сабирачи не изврше операцију сабирања када су секвенце улазних битова велике. Али овде ће дати излаз за било које секвенце улазних битова са одређеним кашњењем. Према дигиталним круговима, ако коло даје излаз са закашњењем, неће бити пожељно. То се може превазићи преносним кругом сабирача који гледа унапред.

![4 једноставна круга преклопних кругова [тестирано]](https://electronics.jf-parede.pt/img/4017-ic-circuits/21/4-simple-clap-switch-circuits.png)