У комбинационим круговима користе се различити логички гејтови за пројектовање кодера, мултиплексера, декодера и де-мултиплексера. Ови кругови имају неке карактеристике као што излаз овог кола углавном зависи од нивоа који су у сваком тренутку на улазним стезаљкама. Ово коло не укључује меморију. Раније стање улаза нема утицаја на тренутно стање овог кола. Улази и излази комбинационог кола су „н“ бр. улаза & 'м' бр. излаза. Неки од комбинационих кругова су напола сабирач и сабирач, одузимач, кодер, декодер, мултиплексер и демултиплексер. Овај чланак говори о прегледу половине сабирача и пуног збрајача и ради са табелама истине.

Шта је Аддер?

Сабирач је дигитално логичко коло у електроници која се широко користи за сабирање бројева. У многим рачунарима и другим врстама процесора, сабирачи се чак користе за израчунавање адреса и сродних активности и израчунавање индекса табела у АЛУ, па чак и за употребу у другим деловима процесора. Они се могу градити за бројне нумеричке приказе попут вишка-3 или бинарно кодиране децимале. Сабирачи су у основи класификовани у две врсте: половично и потпуно збрајање.

Шта је пола аддера и пун аддер круг?

Круг полусабирача има два улаза: А и Б, који додају две улазне цифре и генеришу пренос и збир. Пун круг сабирача има три улаза: А и Ц, који додају три улазна броја и генеришу пренос и збир. Овај чланак даје детаљне информације о томе која је сврха полусабирача и пуни сабирач у табеларним облицима, па чак и у схемама кола. Већ је поменуто да је главна и пресудна сврха сабирача додавање. Испод су детаљи теорија пола сабирача и пуног сабирача.

Основни половични и пуни сабирач

Халф Аддер

Дакле, дошавши до сценарија половине сабирача, он додаје две бинарне цифре где се улазни битови називају повећањем и сабирањем, а резултат ће бити два излаза један је збир, а други носи. Да би се извршила операција збрајања, КСОР се примењује на оба улаза, а АНД улаз се примењује на оба улаза за производњу ношења.

ХА функционални дијаграм

Док у кругу пуног сабирача додаје 3 једнобитна броја, при чему се два од три бита могу назвати операндима, а други назвати као бит унет. Произведени излаз је 2-битни излаз и ови се могу упутити да као излаз носе и зброје.

Коришћењем полусабирача можете да дизајнирате једноставно додавање уз помоћ логичких капија.

Погледајмо пример додавања два појединачна бита.

2-битни табела истине са половином сабирача је као испод:

Табела истине о половини аддера

0 + 0 = 0

0 + 1 = 1

1 + 0 = 1

1 + 1 = 10

То су најмање могуће једнобитне комбинације. Али резултат за 1 + 1 је 10, збирни резултат мора бити преписан као 2-битни излаз. Дакле, једначине се могу записати као

0 + 0 = 00

0 + 1 = 01

1 + 0 = 01

1 + 1 = 10

Излаз „1“ од „10“ је спровођење. „СУМ“ је уобичајени излаз, а „ЦАРРИ“ је изведба.

Сада је разјашњено да се 1-битни сабирач може лако имплементирати уз помоћ КСОР Гате за излаз „СУМ“ и АНД Гате за „Царри“.

На пример, када треба да додамо два 8-битна бајта заједно, онда се то може применити коришћењем логичког кола са пуним сабиром. Полусабирач је користан када желите да додате једну бинарну цифру.

Начин за развијање двобинарних сабирача био би прављење табеле истине и њено смањивање. Када желите да направите сабирник са три бинарне цифре, операција сабирања половичног збрајања изводи се два пута. На сличан начин, када одлучите да направите четвороцифрени сабирач, операција се изводи још једном. Са овом теоријом било је јасно да је примена једноставна, али да развој траје дуго.

Најједноставнији израз користи ексклузивну функцију ОР:

Збир = А КСОР Б.

Носити = А И Б.

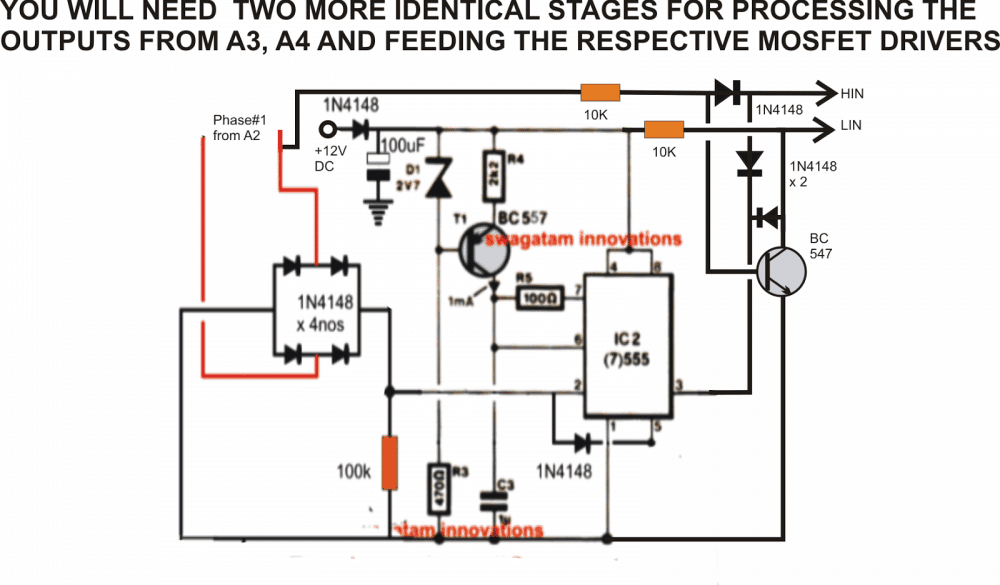

ХА логички дијаграм

А еквивалентан израз у смислу основног И, ИЛИ и НЕ је:

СУМ = А.Б + А.Б ’

ВХДЛ код за пола збрајања

Ентитет је

Порт (а: у СТД_ЛОГИЦ

б: у СТД_ЛОГИЦ

сха: оут СТД_ЛОГИЦ

цха: оут СТД_ЛОГИЦ)

крај ха

Архитектура Понашање горњег кола је

започети

сха<= a xor b

не<= a and b

крај Понашање

ИЦ број са половичним аддером

Имплементација половичног сабирача може се извршити путем интегрисаних кругова брзе ЦМОС дигиталне логике попут серије 74ХЦкк која укључује СН74ХЦ08 (7408) и СН74ХЦ86 (7486).

Ограничења половине аддера

Главни разлог за позивање ових бинарних сабирача као што је Халф Аддерс је тај што не постоји опсег за укључивање преносног бита помоћу ранијег бита. Дакле, ово је главно ограничење ХА-а који су се некада користили попут бинарног сабирача, посебно у ситуацијама у реалном времену које укључују додавање неколико битова. Дакле, ово ограничење се може превазићи коришћењем пуних сабирача.

Фулл Аддер

Овај сабирач је тешко применити у поређењу са половичним збрајачем.

Функционални дијаграм пуног збрајања

Разлика између половичног сабирача и пуног збрајања је у томе што пуни збрајач има три улаза и два излаза, док половични сабирач има само два улаза и два излаза. Прва два улаза су А и Б, а трећи улаз је улаз који се носи као Ц-ИН. Када је дизајнирана логика пуног сабирача, осам их спојите да бисте креирали сабирач у целом бајту и каскадно преносили бит из једног сабирача у други.

ФА табела истине

Излазни пренос је означен као Ц-ОУТ, а нормални излаз је представљен као С што је „СУМ“.

Са наведеним табела истинитог сабирача , примена пуног склопа сабирача може се лако разумети. СУМ „С“ се производи у два корака:

- КСОРингом даних уноса „А“ и „Б“

- Резултат А КСОР Б је тада КСОРед помоћу Ц-ИН-а

Ово генерише СУМ и Ц-ОУТ је тачно само када су два од три улаза ХИГХ, тада ће Ц-ОУТ бити ХИГХ. Дакле, можемо да имплементирамо пуни склоп сабирача уз помоћ два половична склопа сабирача. У почетку ће се половина сабирача користити за додавање А и Б да би се произвео делимични Збир, а логика сабирника друге половине може се користити за додавање Ц-ИН у Збир који је произвео прва половина сабирача да би се добио коначни излаз С

Ако било која од логике половине сабирача изведе пренос, постојаће излазни пренос. Дакле, Ц-ОУТ ће бити функција ИЛИ излаза са половином сабирача. Погледајте имплементацију пуног склопа сабирача приказаног доле.

Логички дијаграм пуног збрајања

Примена већих логичких дијаграма је могућа са горенаведеном логиком пуног сабирања, а једноставнији симбол се углавном користи за представљање операције. Доље је дат једноставнији шематски приказ једнобитног пуног сабирача.

Са овом врстом симбола можемо додати два бита заједно, узимајући ношење из следећег нижег реда величине и шаљући ношење у следећи виши ред величине. У рачунару, за вишебитну операцију, сваки бит мора бити представљен пуним сабирачем и мора се додати истовремено. Дакле, да бисте додали два 8-битна броја, требат ће вам 8 пуних сабирача који се могу формирати каскадним два од 4-битних блокова.

Пола и потпуно сабирање помоћу К-мапе

Чак и излази за збир и пренос за половину сабирача могу се добити и методом Карнаугх-ове мапе (К-мап). Тхе напола сабирач и пуни сабирач логички израз може се добити путем К-мапе. Дакле, К-мапа за ове сабираче је разматрана у наставку.

К-мапа полусабирача је

ХА К-мапа

Пуни додавач К-Мап је

ФА К-мапа

Логички израз СУМ-а и ношења

Логички израз збира (С) може се одредити на основу уноса наведених у табели.

= А’Б’Цин + А ’Б ЦЦин’ + А Б’Цин ’+ АБ Цин

= Цин (А’Б ’+ АБ) + Цин’ (А’Б + А Б ’)

= Цин ЕКС-ОР (А ЕКС-ИЛИ Б)

= (1,2,4,7)

Логички израз ношења (Цоут) може се одредити на основу уноса наведених у табели.

= А’Б Цин + АБ’Цин + АБ Цин ’+ АБЦин

= АБ + БЦин + АЦин

= (3, 5, 6, 7)

Са горе поменутим табелама истине могу се добити резултати и поступак је:

Комбинациони круг комбинује различите капије у колу где то могу бити енкодер, декодер, мултиплексер и демултиплексер . Карактеристике комбинационих кола су следеће.

- Излаз у било ком тренутку се заснива само на нивоима који су присутни на улазним терминалима.

- Не користи меморију. Претходно стање улаза нема никаквог утицаја на тренутно стање кола.

- Може имати било који број улаза и м број излаза.

ВХДЛ кодирање

ВХДЛ кодирање за пуни сабирач укључи следеће.

ентитет фулл_адд је

Порт (а: у СТД_ЛОГИЦ

б: у СТД_ЛОГИЦ

цин: у СТД_ЛОГИЦ

сум: оут СТД_ЛОГИЦ

цоут: оут СТД_ЛОГИЦ)

крај фулл_адд

Архитектура Понашање фулл_адд је

компонента ха је

Порт (а: у СТД_ЛОГИЦ

б: у СТД_ЛОГИЦ

сха: оут СТД_ЛОГИЦ

цха: оут СТД_ЛОГИЦ)

крајња компонента

сигнал с_с, ц1, ц2: СТД_ЛОГИЦ

започети

ХА1: ха карта луке (а, б, с_с, ц1)

ХА2: ха карта луке (с_с, цин, сум, ц2)

трошак<=c1 or c2

крај Понашање

Тхе разлика између половине сабирача и пуног сабирача је да половина сабирача даје резултате, а пуни сабирач користи половину сабирача да би произвео неки други резултат. Слично томе, док је Фулл-Аддер два полу-збрајања, Фулл-Аддер је стварни блок који користимо за стварање аритметичких кола.

Царри Лоокахеад Аддерс

У концепту таласастог склопа за таласање, битови који су неопходни за додавање су одмах доступни. Док сваки одељак сабирача мора задржати своје време за долазак преноса из претходног блока сабирача. Због тога је потребно више времена да се произведе СУМ и НОСИ, јер сваки одељак у колу чека на долазак улаза.

На пример, да би испоручио излаз за н-ти блок, мора да прими улаз од (н-1) -тог блока. И ово кашњење се сходно томе назива закашњењем ширења.

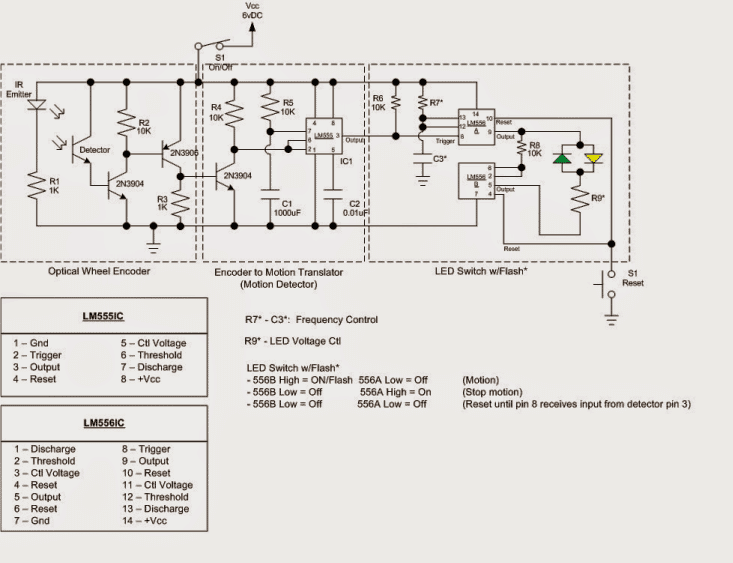

Да би се превазишло кашњење сабирања са валовитим носачима, представљен је сабирник за пренос-лоокахеад. Овде се коришћењем компликованог хардвера може смањити кашњење ширења. Дијаграм доле приказује зброј носача, који користи пуне сабираче.

Носите Лоокахеад користећи Фулл Аддер

Табела истине и одговарајуће излазне једначине су

| ДО | Б. | Ц. | Ц + 1 | Стање |

| 0 | 0 | 0 | 0 | Но Царри Генериши |

| 0 | 0 | 1 | 0 | |

| 0 | 1 | 0 | 0 | |

| 0 | 1 | 1 | 1 | Но Царри Пропагирај |

| 1 | 0 | 0 | 0 | |

| 1 | 0 | 1 | 1 | |

| 1 | 1 | 0 | 1 | Носи Генериши |

| 1 | 1 | 1 | 1 |

Једначина простирања преноси се Пи = Аи КСОР Би, а генерисање преноса је Ги = Аи * Би. Помоћу ових једначина једначине збира и ношења могу се представити као

СУМ = Пи КСОР Ци

Ци + 1 = Ги + Пи * Ци

Ги испоручује пренос само када су оба улаза Аи и Би једнака 1, не узимајући у обзир носивост улаза. Пи је повезан са ширењем ношења од Ци до Ци + 1.

Разлика између половине и пуног збрајања

Тхе разлика између табеле половине сабирача и табеле пуног сабирача приказано је доле.

| Халф Аддер | Фулл Аддер |

| Халф Аддер (ХА) је комбинационо логичко коло и ово коло се користи за додавање две једнобитне цифре. | Фулл Аддер (ФА) је комбинационо коло и ово коло се користи за додавање три једнобитне цифре. |

| У ХА, када се пренос генерише из претходног додавања, не може се додати у следећи корак. | У ФА, када се пренос генерише из ранијег додавања, онда се може додати у следећи корак. |

| Пола сабирача укључује две логичке капије као што су АНД капија и ЕКС-ОР капија. | Потпуни сабирач укључује две ЕКС-ОР капије, две ИЛИ капије и две АНД капије. |

| Улазни битови у полусабиру су два попут А, Б. | Улазни битови у пуном сабирачу су три попут А, Б & Ц-ин |

| Половина зброја и једначина ношења износи С = а⊕б Ц = а * б | Пуни логички израз сабирача је С = а ⊕ б⊕Цин Цоут = (а * б) + (Цин * (а⊕б)). |

| ХА се користи у рачунарима, калкулаторима, уређајима који се користе за дигитално мерење итд. | ФА се користи у дигиталним процесорима, додавању више битова итд. |

Тхе кључне разлике између половине сабирача и пуног сабирача се разматрају у наставку.

- Половина сабирача генерише збир и пренос додавањем два бинарна улаза, док се пуни сабирач користи за генерисање збира и преноса додавањем три бинарна улаза. И хард-архитектура полу-сабирача и потпуно сабирача није иста.

- Главна карактеристика која разликује ХА и ФА је то што у ХА не постоји таква погодба која би последњи додатак сматрала својим уносом. Али, ФА лоцира одређену колону за унос попут Цин-а како би размотрио бит за пренос задњег додавања.

- Два сабирача показаће разлику на основу компонената које се користе у кругу за његову конструкцију. Полусабирачи (ХА-ови) су дизајнирани са комбинацијом две логичке капије попут АНД & ЕКС-ОР, док је ФА дизајниран са комбинацијом три АНД, две КСОР и једне ИЛИ капије.

- У основи, ХА раде на 2-два улаза од 1 бита, док ФА раде на три улаза од 1 бита. Половина сабирача користи се у различитим електронским уређајима за процену сабирања, док се пуни сабирач користи у дигиталним процесорима за додавање дугачког бита.

- Сличности у ова два сабирача су, и ХА и ФА су комбинациони дигитални склопови, тако да не користе ниједан меморијски елемент попут секвенцијалних кола. Ови кругови су од суштинског значаја за аритметичке операције како би се обезбедио сабирање бинарног броја.

Примена потпуног аддера помоћу половине сабирача

Имплементација ФА може се извршити помоћу два полусабирача који су повезани логички. Блок дијаграм овога може се приказати испод који говори о повезивању ФА помоћу два половична сабирача.

Једначине збира и ношења из претходних прорачуна су

С = А ‘Б’ Цин + А ’БЦ’ у + АБЦин

Цоут = АБ + АЦин + БЦин

Једначина збира може се записати као.

Цин (А’Б ‘+ АБ) + Ц‘ ин (А‘Б + А Б ’)

Дакле, зброј = Цин ЕКС-ОР (А ЕКС-ОР Б)

Цин (А ЕКС-ИЛИ Б) + Ц’ин (А ЕКС-ИЛИ Б)

= Цин ЕКС-ОР (А ЕКС-ИЛИ Б)

Цоут се може написати на следећи начин.

ЦОУТ = АБ + АЦин + БЦин.

Цоут = АБ + + разочарења Бцин (А + А)

= АБЦин + АБ + АЦин + А ’Б Цин

= АБ (1 + Цин) + АЦин + А ’Б Цин

= А Б + АЦин + А ’Б Цин

= АБ + АЦин (Б + Б ’) + А’ Б Цин

= АБЦин + АБ + А’Б Цин + А ’Б Цин

= АБ (Цин + 1) + А Б Цин + А ’Б Цин

= АБ + АБ ’Цин + А’ Б Цин

= АБ + Цин (АБ ’+ А’Б)

Према томе, ЦОУТ = АБ + Цин (А ЕКС-ОР Б)

У зависности од горње две једначине збира и ношења, ФА коло се може применити уз помоћ две ХА и ОР капије. Шема кола пуног сабирача са два половична збрајања је илустрована горе.

Потпуни сабирач помоћу две половине сабирача

Дизајн комплетног додавача помоћу НАНД Гатес-а

НАНД капија је једна врста универзалних капија која се користи за извршавање било које врсте логичког дизајна. ФА круг са дијаграмом НАНД капија приказан је доле.

ФА користећи НАНД Гатес

ФА је лаган једнобитни сабирач и ако желимо извршити додавање н-бита, тада н бр. једнобитних ФА-а морају се користити у формату каскадне везе.

Предности

Тхе предности пола сабирача и пуног сабирача укључи следеће.

- Најважнија сврха полусабирача је додавање два једнобитна броја

- Пуни сабирачи садрже могућност додавања преносног бита који је резултат претходног сабирања

- Помоћу пуног сабирача могу се применити кључни склопови попут сабирача, мултиплексера и многих других

- Пун круг сабирача троши минималну снагу

- Предности пуног сабирача у односу на половину сабирача су у томе што се пуни сабирач користи за превазилажење недостатка половичног сабирача, јер се половични сабирач углавном користи за додавање два 1-битна броја. Пола сабирача не додаје носећи бит, па је за превладавање овог пуног збрајања запослено. У Фулл аддер, додавање три бита се може извршити и генерише два излаза.

- Дизајнирање сабирача је једноставно и основни је грађевински блок тако да једнобитни додатак може бити лако разумљив.

- Овај сабирач може се претворити у половину одузимача додавањем претварача.

- Коришћењем пуног сабирача може се постићи висок излаз.

- Брзи

- Веома јак за скалирање напона

Мане

Тхе недостаци половине сабирача и пуног сабирача укључи следеће.

- Поред тога, пола сабирача не може да користи пре ношења, па није применљив за каскадно додавање вишебитних.

- Да би се превазишао овај недостатак, ФА је потребно додати три 1 бита.

- Једном када се ФА користи у облику ланца попут РА (Риппле Аддер), тада се погонска способност излаза може смањити.

Апликације

Примене половине сабирача и потпуног сабирача укључују следеће.

- Додавање бинарних битова може се извршити упола сабирачем користећи АЛУ у рачунару, јер користи сабирач.

- Комбинација половине сабирача може се користити за пројектовање пуног склопа сабирача.

- Пола сабирача користе се у калкулаторима и за мерење адреса као и табела

- Ови кругови се користе за руковање различитим апликацијама у оквиру дигиталних кола. У будућности игра кључну улогу у дигиталној електроници.

- ФА коло се користи као елемент у многим великим круговима као што је Риппле Царри Аддер. Овај сабирач истовремено додаје број битова.

- ФА се користе у јединици за аритметичку логику (АЛУ)

- ФА се користе у апликацијама везаним за графику као што је ГПУ (графичка процесна јединица)

- Они се користе у кругу множења за извршавање множења преноса.

- У рачунару, за генерисање меморијске адресе и изградњу програмског контрапункта према следећим инструкцијама, јединица аритметичке логике се користи помоћу пуних сабирача.

Дакле, кад год се сабере два бинарна броја, тада се бројеви додају у почетку најмање битова. Овај поступак се може извести помоћу полусабирача јер је најједноставнији н / в који омогућава додавање два 1-битна броја. Улази овог сабирача су бинарне цифре, док су излази збир (С) и ношење (Ц).

Кад год је укључен број цифара, тада се мрежа ХА користи само за повезивање најмање цифара, јер ХА не може додати број за ношење из раније класе. Потпуни сабирач може се дефинисати као основа свих дигиталних аритметичких уређаја. Ово се користи за додавање три једноцифрена броја. Овај сабирач укључује три улаза попут А, Б и Цин док су излази Сум и Цоут.

Повезани концепти

Тхе појмови повезани са полусабиром и пуним сабирачем само се не држите једне сврхе. Они се широко користе у многим апликацијама, а неколико сродних је поменуто:

- Пола сабирача и пуни сабирач ИЦ број

- Развој 8-битног сабирача

- Које су мере предострожности за упола сабирање?

- ЈАВА Аплет таласастог носача таласа

Према томе, овде се ради о теорија пола сабирача и пуног сабирача заједно са табелама истине и логичким дијаграмима, приказан је и дизајн пуног сабирача помоћу пола склопа сабирача. Многи од пола сабирача и пуног сабирача пдф доступни су документи који пружају напредне информације о овим концептима. Даље је важно знати како је имплементиран 4-битни пуни сабирач ?