ЕЦЛ (емитерско спрегнута логика) је први пут изумео у ИБМ-у у августу 1956. Ханнон С. Иоурке. Ова логика је такође позната као логика тренутног режима, која се користи у рачунарима ИБМ 7090 и 7094. ЕЦЛ породица је веома брза у поређењу са дигитална логика породице. Генерално, ова логичка породица обезбеђује кашњење пропагације мање од 1 нс. То је логичка породица заснована на транзисторима биполарног споја. То је најбржа логичка фамилија кола која је доступна за пројектовање конвенционалног логичког система. Овај чланак говори о прегледу једног емитерско спрегнуто логичко коло , рад са апликацијама.

Шта је логика спрегнута емитером?

Емитерска логика је најбоља БЈТ -базирана логичка породица која се користи у дизајну конвенционалног логичког система. Понекад се назива и логика тренутног мода, што је дигитална технологија веома велике брзине. Генерално, ЕЦЛ се сматра најбржим логичким ИЦ-ом где постиже свој рад велике брзине коришћењем веома малог напона и такође избегавајући да транзистори уђу у регион засићења.

Имплементација ЕЦЛ-а користи позитиван напон напајања који је познат као ПЕЦЛ или позитивно референтни ЕЦЛ. Код раних ЕЦЛ капија, напајање негативног напона се користи због отпорности на буку. Након тога, позитивно референцирани ЕЦЛ постао је веома познат због својих компатибилнијих логичких нивоа у поређењу са ТТЛ логичким породицама.

Логика повезана са емитером расипа огромну количину статичке снаге, међутим, њена укупна потрошња струје је ниска у поређењу са ЦМОС на високим фреквенцијама. Дакле, ЕЦЛ је углавном користан у круговима за дистрибуцију такта и апликацијама заснованим на високим фреквенцијама.

Логичке карактеристике повезане са емитером

Карактеристике ЕЦЛ-а ће их користити у многим апликацијама заснованим на високим перформансама.

- ЕЦЛ обезбеђује два излаза који су увек комплементарни, јер се рад кола заснива на диференцијалном појачалу.

- Ова логичка породица је углавном погодна за монолитне методе производње јер су логички нивои функција односа отпорника.

- Уређаји ЕЦЛ фамилије генеришу прави и комплементарни излаз предложене функције без употребе спољних претварача. Сходно томе, смањује се број пакета и захтеви за напајањем и такође смањују проблеми који се јављају услед временских кашњења.

- ЕЦЛ уређаји у дизајну диференцијалног појачала нуде широку флексибилност перформанси, тако да ЕЦЛ кола дозвољавају да се користе и као дигитална и као линеарна кола.

- Дизајн ЕЦЛ капије има нормално високу и ниску улазну импедансу, што је изузетно погодно за постизање великог вентилатора као и могућности погона.

- ЕЦЛ уређаји стварају константан одвод струје на извору напајања како би се поједноставио дизајн напајања.

- Уређаји ЕЦЛ укључујући излазе отвореног емитера једноставно им омогућавају да укључе погонски капацитет далековода.

Емитерско склопљено логичко коло

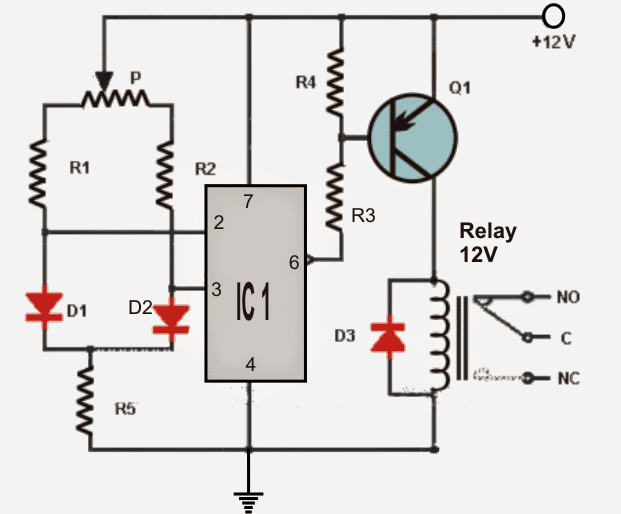

У наставку је приказано логичко коло спрегнуто емитером за инвертор које је дизајнирано са отпорницима и транзисторима. У овом колу, терминали емитера два транзистора су једноставно повезани са отпором за ограничавање струје РЕ који се користи да би се избегло да транзистор уђе у засићење. Овде се излаз транзистора узима са терминала колектора уместо терминала емитера. Ово коло обезбеђује два излаза Воут (инвертујући излаз) и Воут2 (неинвертујући излаз) и улазни терминал попут Вин где се даје високи или ниски улаз. +Вцц = 5В.

Како функционише логика спојених емитера?

Операција логике спрегнуте емитером је да кад год се ВИСОКИ улаз да у ЕЦЛ коло, онда ће транзистор „К1“ укључити, а К2 транзистор ИСКЉУЧЕН, али К1 транзистор није засићен. Дакле, ово ће повући ВОУТ2 излаз на ВИСОКО и вредност ВОУТ1 излаза ће бити НИСКА због пада унутар Р1.

Слично томе, када је ВИН вредност дата ЕЦЛ-у ЛОВ, онда ће К1 транзистор ИСКЉУЧИТИ и К2 транзистор УКЉУЧЕН. Дакле, К2 транзистор неће прећи у засићење. Тако ће ВОУТ1 излаз бити повучен ВИСОК, а ВОУТ2 излазна вредност ће бити ниска због пада унутар отпора Р2.

Да видимо како се транзистор К1 и К2 укључује и гаси када се примени напон.

Два транзистора као што су К1 и К2 у овом колу су повезани као диференцијално појачало помоћу отпорника заједничког емитера.

Напони напајања за овај пример кола су ВЦЦ = 5,0, ВББ = 4,0 & ВЕЕ = 0 В. Улазне вредности високог и ниског нивоа су једноставно дефинисане као 4,4 В и 3,6 В. Заправо, ово коло генерише ЛОВ оутпут & ХИГХ нивое који су за 0,6 волти већи; међутим, ово се исправља у оквиру стварних ЕЦЛ кола.

Када је Вин ХИГХ, онда је К1 транзистор укључен, али није засићен и К2 транзистор је искључен. Дакле, излазни напон попут ВОУТ2 се повлачи на 5 В кроз отпорник Р2 и може се показати да је пад напона на отпорнику Р1 око 0,8 В тако да је ВОУТ1 = 4,2 В (НИСКО). Додатно ВЕ = ВОУТ1 – ВК1 => 4.2В – 0.4В = 3.8В пошто је транзистор К1 потпуно укључен.

Једном када је Вин ЛОВ, К2 транзистор ће бити укључен, али неће бити засићен и К1 транзистор ће се искључити. Према томе, ВОУТ1 се повлачи на 5,0 В помоћу отпорника Р1 и може се показати да је ВОУТ2 4,2 В. Такође ВЕ => ВОУТ2 – ВК2 => 4,2 В – 0,8 В => 3,4 В када је транзистор К2 укључен.

У ЕЦЛ, два транзистора никада нису у засићењу као т Промене улазног/излазног напона су прилично мале попут 0,8в а улазна импеданса је висока, а излазни отпор низак. Ово помаже ЕЦЛ-у да ради брже са краћим временом кашњења ширења.

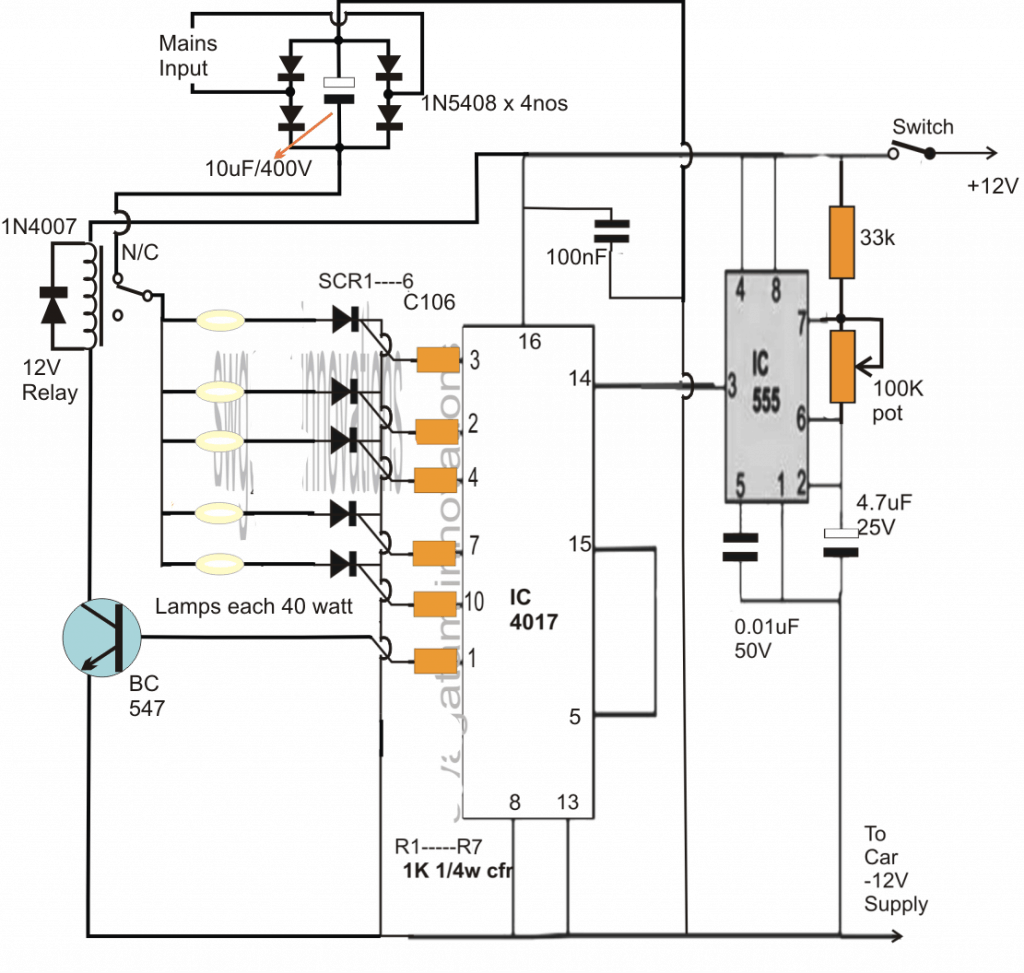

Два улаза емитера спрегнута логичко ИЛИ/НИ коло капије

Логичко коло капије ИЛИ/НИ спојено са два улаза емитера је приказано испод. Ово коло је дизајнирано модификацијом горњег круга претварача. Модификација је додавањем додатног транзистора на улазној страни.

Рад овог кола је веома једноставан. Када су улази примењени на транзисторима К1 и К2 ниски, онда ће излаз 1 (Воут1) учинити ВИСОКОМ. Дакле, овај Воут1 одговара излазу НОР капије.

Истовремено, ако је К3 транзистор укључен, онда ће други излаз (Воут2) учинити ВИСОКИМ. Дакле, овај Воу2 излаз одговара излазу капије ИЛИ.

На исти начин, ако су оба улаза К1 и К2 транзистора ВИСОКА, онда ће се укључити К1 и К2 транзистор и обезбедити ниски излаз на ВОУТ1 терминалу.

Ако је К3 транзистор искључен током ове операције, онда ће обезбедити висок излаз на ВОУТ2 терминалу. Дакле, табела истинитости за капију ИЛИ/НИ је дата испод.

|

Инпутс |

Инпутс | ИЛИ |

НОР |

|

А |

Б | И | И |

|

0 |

0 | 0 | 1 |

|

0 |

1 | 1 |

0 |

| 1 | 0 | 1 |

0 |

| 1 | 1 | 1 |

0 |

Логичке карактеристике спрегнуте емитером

Карактеристике ЕЦЛ-а укључују следеће.

- У поређењу са ТТЛ, ЕЦЛ има брже време пропагације у распону од 0,5 до 2 нс. Али, емитерска логичка дисипација снаге је већа у поређењу са ТТЛ-ом, попут 30 мВ.

- И/О напони ЕЦЛ-а имају мали замах попут 0,8.

- Улазна импеданса ЕЦЛ-а је висока и излазни отпор је низак; сходно томе, транзистор веома брзо мења своја стања.

- Капацитет вентилатора ЕЦЛ-а је висок, а кашњења гејта су мала.

- О/п логика ЕЦЛ се мења из ЛОВ у високо стање, али нивои напона за ова стања ће варирати између ТТЛ и ЕЦ.

- Отпорност на буку ЕЦЛ-а је 0,4В.

Предности и мане

Тхе предности емитерске логике се разматрају у наставку.

- Фаноут ЕЦЛ-а је 25 што је боље у поређењу са ТТЛ-ом и ниско је у поређењу са ЦМОС-ом.

- Просечно време кашњења пропагације ЕЦЛ-а је 1 до 4 нс што је боље у поређењу са ЦМОС и

- ТТЛ. Тако се зове најбржа логичка породица.

- Када су БЈТ-ови у емитеру спојени логичке капије раде у активном региону, тада имају максималну брзину у поређењу са свим логичким породицама.

- ЕЦЛ капије генеришу комплементарне излазе.

- У водовима напајања нема струјних прекидача.

- Излази се могу спојити заједно да би се обезбедила функција жичаног ИЛИ.

- Параметри ЕЦЛ-а се не мењају много кроз температуру.

- Не. број функција доступних са јединог чипа је висок.

Тхе недостаци логике спрегнуте емитером се разматрају у наставку.

- Има изузетно мању маргину буке, тј. ±200 мВ.

- Расипање снаге је велико у поређењу са другим логичким капијама.

- За повезивање са другим логичким породицама, неопходни су мењачи нивоа.

- Фаноут ограничава капацитивно оптерећење.

- У односу на ТТЛ , ЕЦЛ капије су скупе.

- У поређењу са ЦМОС & ТТЛ, ЕЦЛ отпорност на буку је најгора.

Апликације

Примене логике спрегнуте емитером укључују следеће.

- Емитерско спрегнута логика се користи као логичка и интерфејс технологија у оквиру изузетно брзих комуникационих уређаја као што су интерфејси примопредајника са оптичким влакнима, Етхернет & АТМ (асинхрони режим преноса) мреже.

- ЕЦЛ је логичка породица заснована на БЈТ где се његов рад велике брзине може постићи коришћењем релативно малог напона и избегавањем да транзистори пређу у област засићења.

- ЕЦЛ се користи за прављење АСЛТ кола унутар ИБМ 360/91.

- ЕЦЛ избегава коришћење наслаганих транзистора коришћењем једностраног биас и/п и позитивне повратне везе између примарних и секундарних транзистора да би се постигла функција претварача.

- ЕЦЛ се користи у електроници изузетно велике брзине.

Дакле, ово је преглед емитерске спрегнуте логике или ЕЦЛ – коло, рад, карактеристике, карактеристике и апликације. ЕЦЛ је најбржа логичка породица заснована на БЈТ-у у поређењу са другим дигиталним логичким породицама. Своју максималну брзину постиже коришћењем малог замаха напона и избегавањем померања транзистора у област засићења. Ова логичка породица обезбеђује невероватно кашњење пропагације од 1нс, а у најновијим ЕЦЛ породицама, ово кашњење је смањено. Ево питања за вас, који је алтернативни назив за ЕЦЛ?