РИСЦ В је архитектура скупа инструкција коју је развио Универзитет Калифорније, Беркли. Концепт РИСЦ-а је био мотивисан истином да већина компјутерских програма није користила већину инструкција процесора. Дакле, непотребна логика декодирања се користила у дизајну процесори , трошећи више енергије као и површину. Да бисте скратили скуп инструкција и уложили више у ресурсе регистра, РИСЦ В процесор је спроведено.

Ову технологију су приметили многи технолошки гиганти и почетници јер је потпуно отвореног кода и бесплатна. Већина типова процесора је доступна уз уговор о лиценци, али са овом врстом процесора; свако може да направи свој нови дизајн процесора. Дакле, овај чланак разматра преглед РИСЦ В процесора – рад и његове примене.

Шта је РИСЦ В процесор?

У РИСЦ В процесору, термин РИСЦ означава „рачунар са смањеним скупом инструкција“ који извршава неколико рачунарских инструкција, док „В“ означава 5. генерацију. То је хардверска ИСА (архитектура скупа инструкција) отвореног кода заснована на утврђеном принципу РИЗИК .

У поређењу са другим ИСА дизајном, овај ИСА је доступан уз лиценцу отвореног кода. Дакле, бројне производне компаније су најавиле и такође обезбедиле РИСЦ-В хардвер, са оперативним системима отвореног кода.

Ово је нова архитектура и доступна је у отвореним, неограничавајућим и бесплатним лиценцама. Овај процесор има опсежну подршку из индустрије произвођача чипова и уређаја. Дакле, углавном је дизајниран да буде слободно проширив и прилагодљив за употребу у многим апликацијама.

РИСЦ В Историја

РИСЦ је изумео проф. Давид Паттерсон око 1980. године на Универзитету Калифорније, Беркли. Проф. Давид и проф. Јохн Хеннесси представили су своје напоре у две књиге и то „Организација рачунара и дизајн“ и „Архитектура рачунара на Универзитету Станфорд. Дакле, добили су АЦМ А.М. Тјурингова награда за 2017.

Од 1980. до 2010. године започето је развојно истраживање пете генерације РИСЦ-а и коначно је идентификовано као РИСЦ-В што се изговара као ризик пет.

РИСЦ В Архитектура и рад

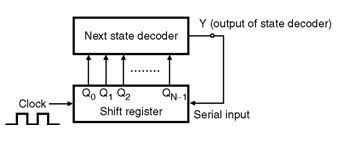

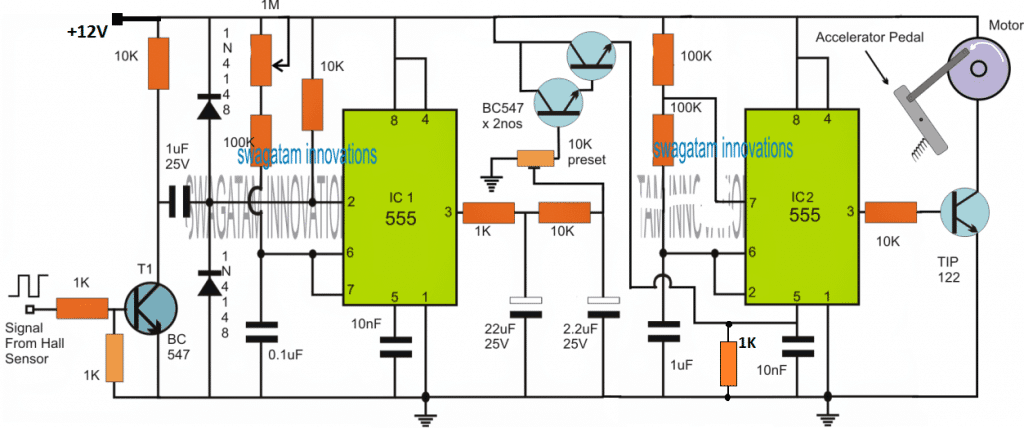

Архитектура РВ12 РИСЦ В приказана је испод. РВ12 је веома конфигурабилан са једнојезгреним РВ32И и РВ64И компатибилним РИСЦ ЦПУ-ом који се користи у уграђеним пољима. РВ12 је такође из 32 или 64-битне ЦПУ породице у зависности од индустријског стандардног РИСЦ-В скупа инструкција.

РВ12 једноставно извршава харвардску архитектуру за истовремени приступ инструкцији као и меморији података. Такође укључује 6-степени цевовод који помаже у оптимизацији преклапања између извршавања, као и приступа меморији ради побољшања ефикасности. Ова архитектура углавном укључује предвиђање гранања, кеш података, јединицу за отклањање грешака, кеш инструкција и опционе јединице множитеља или разделника.

Главне карактеристике РВ12 РИСЦ В укључују следеће.

- То је стандардни сет инструкција у индустрији.

- Параметризовано са 32 или 64-битним подацима.

- Има прецизне и брзе прекиде.

- Прилагођена упутства дозвољавају додавање власничког хардверског акцелератора.

- Извођење једног циклуса.

- Шестостепени цевовод са преклопљеним оптимизацијом.

- Подршка за заштиту меморије.

- Опциони или параметризовани кеш меморије.

- Ектремели Параметеризед.

- Корисници могу да изаберу 32/64-битне податке и јединицу за предвиђање грана.

- Корисници могу да изаберу кеш меморије инструкција/података.

- Структура, величина и архитектура кеша коју може изабрати корисник.

- Подршка за хардверски делилац или множилац према кориснички дефинисаном кашњењу.

- Архитектура магистрале је флексибилна и подржава Висхбоне & АХБ.

- Овај дизајн оптимизује снагу и величину.

- Дизајн је потпуно параметризован што обезбеђује компромисе између перформанси или снаге.

- ЦЛК дизајн за смањење снаге.

- Софтверска подршка по индустријским стандардима.

- Архитектонски симулатор.

- Ецлипсе ИДЕ се користи за Линук/Виндовс.

РИСЦ В Екецутион Пипелине

Укључује пет фаза као што су ИФ (дохваћање инструкције), ИД (декодирање инструкције), ЕКС (извршавање), МЕМ (приступ меморији) и ВБ (повратни упис регистра).

Инструцтион Фетцх

У фази преузимања инструкције или ИФ, једна инструкција се чита са програмског бројача (ПЦ) и меморије инструкција која се ажурира на следећу инструкцију.

Инструкција Пре-Децоде

Када је РВЦ подршка дозвољена, фаза претходног декодирања инструкција ће декодирати 16-битну компресовану инструкцију у изворну 32-битну инструкцију.

Декодирање инструкција

У фази декодирања инструкција (ИД), регистарска датотека је дозвољена и контроле заобилажења су одлучене.

Извршити

У фази извршења, резултат се израчунава за АЛУ, ДИВ, МУЛ инструкцију, меморија дозвољена за инструкцију Сторе или Лоад, а гране и скокови се мере у односу на очекиване резултате.

Меморија

У овој фази меморије, меморији се приступа преко цевовода. Укључивање ове фазе осигурава високе перформансе цевовода.

Одговорити

У овој фази, резултат фазе извршења се уписује у датотеку регистра.

Бранцх Предицтор

Овај процесор укључује јединицу за предвиђање гранања или БПУ који се користи за складиштење прошлих података како би водио РИСЦ В процесор у одлучивању да ли ће се одређена грана узети или не-. Ови предикторски подаци се једноставно ажурирају када се грана изврши.

Ова јединица укључује различите параметре који одређују њено понашање. На пример, ХАС_БПУ се користи да одреди да ли грана предвиђа да је јединица присутна, БПУ_ГЛОБАЛ_БИТС ће одредити колико прошлих битова треба да се користи, а БПУ_ЛОЦАЛ_БИТС ће одредити колико ЛСБ-а програмског бројача треба да се користи. Комбинација БПУ_ЛОЦАЛ_БИТС & БПУ_ГЛОБАЛ_БИТС ће створити вектор који се углавном користи за адресирање табеле предвиђања грана.

Кеш података

Ово се углавном користи за убрзавање приступа меморији података баферовањем новоприступљених локација меморије. Ово може да обрађује приступе полуречи, бајтовима и речима када је КСЛЕН = 32 ако се налазе на сопственим границама. Такође је способан да рукује приступима полуречи, бајтовима, речима и двоструким речима када је КСЛЕН=64 ако су на сопственим границама.

Током пропуста кеша, цео блок се може записати назад у меморију, тако да ако је потребно, нови блок се може учитати у кеш меморију. Кеш података је онемогућен постављањем ДЦАЦХЕ_СИЗЕ на нулу. Након тога, меморијским локацијама се приступа директно преко Дата Интерфаце .

Кеш инструкција

Ово се углавном користи за убрзавање преузимања инструкција баферовањем новопреузетих инструкција. Ова кеш меморија се користи за преузимање једне парцеле за сваки циклус на било којој 16-битној граници, али не преко границе блока. Током пропуста кеша, цео блок се може учитати из меморије инструкција. Конфигурација ове кеш меморије се може извршити на основу потреба корисника. Величина кеша, алгоритам замене и дужина блока се могу конфигурисати.

Циклус инструкција ће бити онемогућен постављањем ИЦАЦХЕ_СИЗЕ на нулу. Након тога, пакети се преузимају директно из меморије преко Инструцтион Интерфаце.

Јединица за отклањање грешака

Јединица за отклањање грешака ће омогућити окружењу за отклањање грешака да се заустави и испита ЦПУ. Главне карактеристике овога су праћење грана, праћење у једном кораку до 8 хардверских тачака прекида.

Регистер Филе

Ово је дизајнирано са 32 локације регистра од Кс0 до Кс31 где је Кс9 регистар увек нула. Датотека регистра укључује 1 порт за писање и 2 порта за читање.

Цонфигурабле Интерфаце

Ово је спољни интерфејс где овај процесор подржава различите спољне интерфејсе магистрале.

Како РИСЦ В функционише?

РИСЦ-В је архитектура скупа инструкција заснована на принципима РИСЦ (компјутер са смањеним скупом инструкција). Овај процесор је веома јединствен и такође револуционаран јер је бесплатна, уобичајена ИСА отвореног кода где се хардвер може развити, софтвер може бити портован и процесори могу бити дизајнирани да га подржавају.

Разлика Б/В РИСЦ В вс МИПС

Разлика између РИСЦ В и МИПС укључује следеће.

|

РИСЦ В |

МИПС |

| Термин РИСЦ В је скраћеница за рачунар са смањеним скупом инструкција где је „В“ пета генерација. | Термин 'МИПС' значи 'милион инструкција у секунди'. |

| РИСЦ-В једноставно дозвољава произвођачима мањих уређаја да дизајнирају хардвер без плаћања. | МИПС омогућава произвођачу да измери брзину процесора плаћањем јер није бесплатан. |

| МИПС је ефикасно мртав. | РИСЦ-В није ефикасно мртав. |

| Овај процесор даје упутства за гранање за поређење два регистра. | МИПС зависи од инструкције поређења која лоцира регистар на 1 или 0 на основу тога да ли је контраст истинит. |

| ИСА шема кодирања је фиксна и променљива у РИСЦ В. | ИСА шема кодирања је фиксна у МИПС-у |

| Величина скупа инструкција је 16-битна или 32-битна или 64-битна или 128-битна. | Величина скупа инструкција је 32-битна или 64-битна. |

| Има 32 опште намене и регистра са покретним зарезом | Има 31 регистар опште намене и са помичним зарезом. |

| Има 26 операција са помичним зарезом једноструке и двоструке прецизности. | Има 15 једноструких и двоструких прецизних операција са плутајућим зарезом. |

Разлика Ч/Б РИСЦ В вс АРМ

Разлика између РИСЦ В и АРМ-а укључује следеће.

|

РИСЦ В |

АРМ |

| РИСЦ-В је отвореног кода, тако да не захтева никакву лиценцу. | АРМ је затворен извор, па му је потребна лиценца. |

| То је нова процесорска платформа, тако да постоји врло мала подршка за софтверска и програмска окружења. | АРМ има веома велику онлајн заједницу, која подржава библиотеке и структуре за помоћ циљним дизајнерима на различитим платформама као што су микропроцесори, микроконтролери и такође сервери. |

| РИСЦ В чипови користе 1 ват снаге. | Чипови засновани на АРМ-у користе снагу испод 4 вата. |

| Има фиксни и варијабилни ИСА систем кодирања. | Има фиксни ИСА систем кодирања. |

| Величина скупа инструкција РИСЦ В креће се од 16-бита до 128-бита. | Величина његове инструкције се креће од 16-бита до 64-бита. |

| Укључује 32 опште намене и регистра са покретним зарезом. | Укључује 31 регистар опште намене и са помичним зарезом. |

| Има 26 појединачних прецизних операција са плутајућим зарезом. | Има 33 појединачне прецизне операције са плутајућим зарезом. |

| Има 26 двоструко прецизних операција са плутајућим зарезом. | Има 29 операција са помичним зарезом двоструке прецизности. |

РИСЦ В Верилог код

Верилог код меморије инструкција за РИСЦ је приказан испод.

// Верилог код за РИСЦ процесор

// Верилог код за меморију инструкција

модул Инструцтион_Мемори(

улаз [15:0] пц,

оутпут[15:0] инструкција

);

рег [`цол – 1:0] меморија [`ров_и – 1:0];

жица [3 : 0] ром_аддр = пц [4 : 1];

почетни

почети

$реадмемб(./тест/тест.прог”, меморија,0,14);

крај

додели инструкцију = меморија[ром_аддр];

ендмодуле

Верилог код за 16-битни РИСЦ В процесор:

модул Рисц_16_бит(

инпут цлк

);

вире јумп,бне,бек,мем_реад,мем_врите,алу_срц,рег_дст,мем_то_рег,рег_врите;

жица [1:0] алу_оп;

жица [3:0] опцоде;

// Пут података

Датапатх_Унит ДУ

(

.цлк(цлк),

.јумп(скок),

.жаба (жаба),

.мем_реад(мем_реад),

.мем_врите(мем_врите),

.алу_срц(алу_срц),

.рег_дст(рег_дст),

.мем_то_рег(мем_то_рег),

.рег_врите(рег_врите),

.бне(бне),

.алу_оп(алу_оп),

.опцоде(опцоде)

);

// контролна јединица

Цонтрол_Унит цонтрол

(

.опцоде(опцоде),

.рег_дст(рег_дст),

.мем_то_рег(мем_то_рег),

.алу_оп(алу_оп),

.јумп(скок),

.бне(бне),

.жаба (жаба),

.мем_реад(мем_реад),

.мем_врите(мем_врите),

.алу_срц(алу_срц),

.рег_врите(рег_врите)

);

ендмодуле

Сетови инструкција

О РИСЦ В скуповима инструкција се говори у наставку.

Аритметичке операције

РИСЦ В аритметичке операције су наведене у наставку.

| Мнемонички | Тип | Упутство | Опис |

| ДОДАЈ рд, рс1, рс2 |

Р |

Додати | рдß рс1 + рс2 |

| СУБ рд, рс1, рс2 |

Р |

Одузми | рдß рс1 – рс2 |

| АДДИ рд, рс1, имм12 |

И |

Додајте одмах | рдß рс1 + имм12 |

| СЛТ рд, рс1, рс2 |

Р |

Поставите мање од | рдß рс1 -< рс2 |

| СЛТИ рд, рс1, имм12 |

И |

Поставите мање него одмах | рдß рс1 -< имм12 |

| СЛТУ рд, рс1, рс2 |

Р |

Поставите мање од непотписано | рдß рс1 -< рс2 |

| СЛТИУ рд, рс1, имм12 |

И |

Поставите мање од тренутног без потписа | рдß рс1 -< имм12 |

| ЛУИ рд, имм20 |

ИН |

Одмах учитајте горњи део | рдß имм20<<12 |

| АУИП рд,имм20 |

ИН |

Додајте горњи непосредан на рачунар | рдß ПЦ+имм20<<12 |

Логичке операције

РИСЦ В логичке операције су наведене у наставку.

| Мнемонички | Тип | Упутство | Опис |

| И рд, рс1, рс2 |

Р |

И | рдß рс1 & рс2 |

| ОР рд, рс1, рс2 |

Р |

ИЛИ | рдß рс1 | рс2 |

| КСОР рд, рс1, рс2 |

Р |

БЕСПЛАТНО | рдß рс1 ^ рс2 |

| АНДИ рд, рс1, имм12 |

И |

И одмах | рдß рс1 & имм2 |

| ОРИ рд, рс1, имм12 |

И |

ИЛИ Одмах | рдß рс1 | имм12 |

| ОКСРИ рд, рс1, имм12 |

И |

КСОР одмах | рдß рс1 ^ рс2 |

| СЛЛ рд, рс1, рс2 |

Р |

Логички помак улево | рдß рс1 << рс2 |

| СРЛ рд, рс1, рс2 |

Р |

Логички помак удесно | рдß рс1 >> рс2 |

| РАС рд, рс1, рс2 |

Р |

Аритметика померања удесно | рдß рс1 >> рс2 |

| СЛЛИ рд, рс1, схамт |

И |

Схифт лево логички одмах | рдß рс1 << схамт |

| СРЛИ рд, рс1, схамт |

И |

Логички померање удесно одмах | рдß рс1 >> схамт |

| СРАИ рд, рс1, схамт |

И |

Аритметика померања удесно одмах | рдß рс1 >> схамт |

Операције учитавања/складишта

Операције учитавања/складишта РИСЦ В су наведене у наставку.

| Мнемонички | Тип | Упутство | Опис |

| ЛД рд, имм12 (рс1) |

И |

Учитај двоструку реч | рдß мем [рс1 +имм12] |

| ЛВ рд, имм12 (рс1) |

И |

Учитај реч | рдß мем [рс1 +имм12] |

| ЛХ рд, имм12 (рс1) |

И |

Учитајте до пола | рдß мем [рс1 +имм12] |

| ЛБ рд, имм12 (рс1) |

И |

Учитај бајт | рдß мем [рс1 +имм12] |

| ЛВУ рд, имм12 (рс1) |

И |

Учитајте реч без потписа | рдß мем [рс1 +имм12] |

| ЛХУ рд, имм12 (рс1) |

И |

Учитајте пола речи без потписа | рдß мем [рс1 +имм12] |

| ЛБУ рд, имм12 (рс1) |

И |

Учитај бајт без потписа | рдß мем [рс1 +имм12] |

| СД рс2, имм12 (рс1) |

С |

Чувајте двоструку реч | рс2 у мем [рс1 +имм12] |

| СВ рс2, имм12 (рс1) |

С |

Чувајте реч | рс2 (31:0) за мем [рс1 +имм12] |

| СХ рс2, имм12 (рс1) |

С |

Чувајте на пола пута | рс2 (15:0) за мем [рс1 +имм12] |

| СБ рс2, имм12 (рс1) |

С |

Чувајте бајт | рс2 (15:0) за мем [рс1 +имм12] |

| СРАИ рд, рс1, схамт |

И |

Аритметика померања удесно одмах | рс2 (7:0) за мем [рс1 +имм12] |

Операције гранања

Операције гранања РИСЦ В су наведене у наставку.

| Мнемонички | Тип | Упутство | Опис |

| БЕК рс1, рс2, имм12 |

СБ |

Грана једнака | Ако је рс1== рс2 ПЦ ß ПЦ+имм12 |

| БНЕ рс1, рс2, имм12 |

СБ |

Огранак није једнак | Ако је рс1!= рс2 ПЦ ß ПЦ+имм12 |

| БГЕ рс1, рс2, имм12 |

СБ |

Грана већа или једнака | Ако је рс1>= рс2 ПЦ ß ПЦ+имм12 |

| БГЕУ рс1, рс2, имм12 |

СБ |

Грана је већа или једнака неозначеном | Ако је рс1>= рс2 ПЦ ß ПЦ+имм12 |

| БЛТ рс1, рс2, имм12 |

СБ |

Огранак мање од | Ако је рс1< рс2 ПЦ ß ПЦ+имм12 |

| БЛТУ рс1, рс2, имм12 |

СБ |

Грана мање од непотписано | Ако је рс1< рс2 ПЦ ß ПЦ+имм12 <<1 |

| ЈАЛ рд, имм20 |

УЈ |

Скочи и повежи | рдßПЦ+4 ПЦß ПЦ+имм20 |

| ЈАЛР рд, имм12(рс1) |

И |

Јумп анд Линк регистер | рдßПЦ+4 ПЦß рс1+имм12 |

Предности

Тхе предности РИСЦ-а В процесор укључи следеће.

- Коришћењем РИСЦВ-а можемо уштедети време за развој, развој софтвера, верификацију итд.

- Овај процесор има много предности попут једноставности, отворености, модуларности, чистог дизајна и проширивости.

- Ово је подржано од стране неколико компајлера језика као што је ГЦЦ (ГНУ Цомпилер Цоллецтион), компајлер бесплатног софтвера и преко Линук ОС .

- Компаније ово могу слободно да користе због тантијема, лиценцних накнада и обавеза.

- РИСЦ-В процесор не укључује нове или иновативне карактеристике јер једноставно следи утврђене принципе РИСЦ-а.

- Слично неколико других ИСА, ова спецификација процесора једноставно дефинише различите нивое скупа инструкција. Дакле, ово садржи 32 и 64-битне варијанте, као и екстензије које пружају подршку за инструкције са помичним зарезом.

- Они су бесплатни, једноставни, модуларни, стабилни итд.

Недостаци

Тхе недостаци РИСЦ В процесора укључи следеће.

- Компајлери и програмери често користе сложена упутства.

- О/п РИСЦ-а се може променити на основу кода када наредне инструкције унутар петље зависе од раније инструкције за извршење.

- Ови процесори морају брзо да сачувају различите инструкције, што захтева велики сет кеш меморије да би благовремено реаговао на инструкције.

- Комплетне карактеристике, могућности и предности РИСЦ-а углавном зависе од архитектуре.

Апликације

Тхе апликације РИСЦ В процесор укључи следеће.

- РИСЦ-В се користи у уграђеним системима, вештачкој интелигенцији и машинском учењу.

- Ови процесори се користе у апликацијама за уграђене системе засноване на високим перформансама.

- Овај процесор је прикладан за употребу у неким одређеним областима као што су ивично рачунарство, АИ и апликације за складиштење.

- РИСЦ-В је важан јер омогућава мањим произвођачима уређаја да дизајнирају хардвер без плаћања.

- Овај процесор једноставно омогућава истраживачима и програмерима да дизајнирају и истражују са бесплатно доступном архитектуром ИСА или скупа инструкција.

- Примене РИСЦ В се крећу од малих уграђених микроконтролера до десктоп рачунара и суперрачунара укључујући векторске процесоре.

Дакле, ово је преглед РИСЦ В процесора – архитектура, рад са апликацијама. Ево питања за вас, шта је ЦИСЦ процесор?