МицроБлазе процесор је развијен 2002. године да интегрише неколико компликованих карактеристика како би задовољио нове, као и растућу потражњу тржишта. Дакле, МицроБлазе процесор је суштински елемент унутар Лов-Енд портфолиа компаније Ксилинк како би се омогућио бржи развој система који садржи Артик®-7 ФПГАс , Спартан®-6, Зинк®-7000 АП СоЦс. Овај процесор је изузетно конфигурабилан, тако да се може користити као уграђени процесор или микроконтролер унутар ФПГА, а такође се може користити и као копроцесор у Зинк-7000 АП СоЦ-овима заснованим на АРМ Цортек-А9. Овај чланак даје кратке информације о МицроБлазе процесор – архитектура и рад са апликацијама.

Шта је Мицроблазе процесор?

Меки микропроцесор који је дизајниран углавном за ФПГА компаније Ксилинк познат је као МицроБлазе процесор. Овај процесор је једноставно имплементиран у оквиру меморије и логичке структуре опште намене ФПГА-а компаније Ксилинк. Овај процесор је сличан ДЛКС архитектури заснованој на РИСЦ-у и има флексибилан систем међусобног повезивања тако да подржава различите уграђене апликације. Главна И/О магистрала и АКСИ интерконекција МицроБлазе је меморијско мапирана трансакциона магистрала са могућношћу мастер-славе.

МицроБлазе користи наменску ЛМБ магистралу за приступ локалној меморији и обезбеђује брзо складиштење на чипу. Многи делови овог процесора се могу конфигурисати од стране корисника као што су величина кеш меморије, дубина јединице за управљање меморијом цевовода, уграђене периферије и интерфејси магистрале.

Мицроблазе Феатурес

Тхе карактеристике Мицроблаза е укључују следеће. Има 32 регистра опште намене.

- Има 32-битне инструкцијске речи укључујући 2 начина адресирања и 3 операнда.

- Адресна магистрала је 32-битна.

- Има 3-степени цевовод или 5-степени цевовод.

- АЛУ блок јединица са мењачем.

- Харвардска архитектура укључује 32-битне податке и адресну магистралу.

- Интерфејс података & ЛМБ или инструкција локалне меморијске магистрале.

- АКС14 и АКС14 стреам интерфејси.

- Јединица са помичним зарезом и јединица за управљање меморијом.

- Подржава лоцкстеп.

- Интерфејс за отклањање грешака и праћење.

Мицробазе Арцхитецтуре

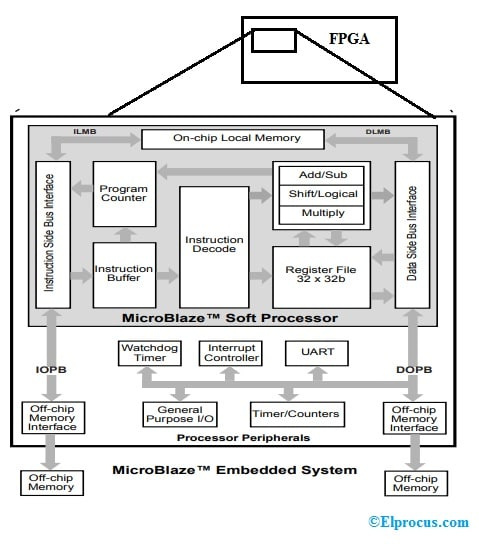

Блок дијаграм МицроБлазе процесора је приказан испод. Овај МицроБлазе процесор је изузетно прилагодљив и подржава преко 70 опција дизајна. Ова архитектура показује трајне хардверске карактеристике као и конфигурабилне опције као што су кеш инструкција или података, јединица за управљање меморијом, јединица са плутајућим зарезом, итд.

Ан уграђени систем састављена око МицроБлазе процесора углавном укључује МицроБлазе Софт процесорско језгро, локалну меморију на чипу, међуконекције стандардне магистрале и ОПБ периферне уређаје (периферна сабирница на чипу). МицроБлазе процесорски систем се углавном креће од језгра процесора помоћу локалне меморије до великог система који укључује неколико МицроБлазе процесори , екстерну меморију и многе ОПБ периферије.

Меко језгро процесора

Меко процесорско језгро МицроБлазе је централно за МицроБлазе уграђени систем. Ово је веома брз и ефикасан 32-битни РИСЦ процесор који има следеће карактеристике.

- Скуп инструкција је ортогонални.

- Одвојене сабирнице података и инструкција.

- 32-битни регистри опште намене.

- Има опциони комплетан 32-битни мењач цеви.

- Уграђени интерфејси за брзу ОЦМ или меморију на чипу и ИБМ-ов индустријски стандард ОПБ (периферна магистрала на чипу).

Имплементације унутар Виртек-ИИ и каснијих уређаја подржавају вишеструки хардвер.

Локална меморија на чипу

Синхрона меморија је локална меморија која се углавном користи за омогућавање блок РАМ-а на чипу.

Стандардне аутобуске интерконекције

Интерфејси магистрале на страни инструкција и података укључују интерфејс за локалну меморију који се назива ЛМБ (Лоцал Мемори Бус) и интерфејс за периферну сабирницу на чипу компаније ИБМ. Тако можемо да дизајнирамо системе који се стриктно придржавају архитектуре Харварда, у супротном, да бисмо поделили ресурсе, можемо да користимо један ОПБ у комбинацији преко арбитра магистрале.

Локална меморијска магистрала даје сигуран унос у једном циклусу за блок РАМ на чипу. Ово је веома ефикасан, једноставан и са једним главним протоколом магистрале и савршен је за повезивање брзе локалне меморије. ОПБ или периферна магистрала на чипу је 32-битна широка мулти-мастер магистрала која је савршена за уједињење периферних уређаја и спољашње меморије са језгром МицроБлазе процесора.

Периферне периферне магистрале на чипу

Хардверски систем МицроБлазе је употпуњен ОПБ периферијама како би се обезбедиле различите функције као што су Ватцхдог тајмер или временска база, тајмер опште намене или бројачи, ИЦ (контролер прекида), различити контролери као што су СРАМ, флеш меморија, ЗБТ меморија, БРАМ, ДДР, СДРАМ, УАРТ Лите , СПИ, И2Ц, У/И опште намене, УАРТ 16450/550 и Етхернет 10/100 МАЦ. Поред тога, такође можемо да додамо и дефинишемо периферне уређаје углавном за прилагођене функције, иначе, интерфејс за дизајн који постоји у ФПГА.

Мицроблазе Сет инструкција

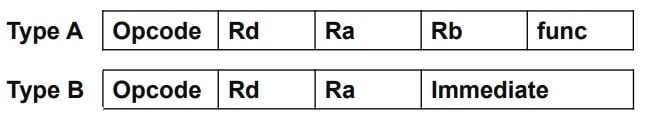

Мицроблазе скупови инструкција су аритметика, логика, гранање, учитавање/складиштење и други. Величина свих упутстава је фиксна. Као операнди се могу дати највише 3 регистра. Мицроблазе укључује два формата инструкција Тип А и Тип Б који су приказани испод.

Формат инструкција типа А се углавном користи за инструкције регистра-регистра. Дакле, укључује операцијски код, једно одредиште и два изворна регистра. Формат инструкција типа Б се углавном користи за непосредне инструкције регистра које укључују опкод, једно одредиште и регистре једног извора.& 16-битни извор тренутне вредности.

У горња два формата инструкција, код операције је код операције, Рд је одредишни регистар који је кодиран са 5-бита, Ра и Рб су изворни регистри од којих је сваки кодиран са 5-бита, а Иммедиате је 16-битна вредност.

Аритметичка упутства

У наставку су дата аритметичка упутства типа А и типа Б.

Укуцате

|

ДОДАЈ Рд, Ра, Рб додати |

Рд = Ра+Рб, погођена заставица за ношење |

|

ДОДАТИ К Рд, Ра, Рб Додајте и наставите да носите |

Рд = Ра+Рб, заставица за ношење није погођена |

| РСУБ Рд, Ра, Рб Обрнуто одузимање |

Рд = Р-Рб, заставица за ношење није погођена |

Тип Б

|

ДОДАЈ И Рд, Ра, Имм додати одмах |

Рд = Ра+сигнЕктенд32 (Имм) |

|

ДОДАТИ ИК Рд, Ра, Имм додајте одмах и наставите да носите |

Рд = Ра+ знак Прошири32 (Имм) |

| РСУБИК Рд, Ра, Имм обрнуто одузимање са непосредним |

Рд = Ра+ сигнЕктенд32 (Имм) -Ра |

| СРА Рд, Ра аритметички померање удесно |

Рд = (Ра>>1) |

Логиц Инструцтионс

Логичка упутства типа А и типа Б су дата у наставку.

Укуцате

|

ИЛИ Рд, Ра, Рб Логично или |

Рд = Ра| Рб |

|

И Рд,Ра,Рб Логичан додатак |

Рд = Ра & Рб |

| КСОР Рд, Ра, Рб Логоицал кор |

Рд = Рб ^ Рб |

| АНДН Рд, Ра, Рб Логично и не |

Рд = Ра & (Рб) |

Тип Б

|

ОРИ Рд, Ра, Имм логичко ИЛИ са непосредним |

Рд = Ра | сигнЕктенд32 (Имм) |

| АНДИ Рд, Ра, Имм логично И са непосредним |

Рд = Ра & сигнЕктенд32 (Имм) |

| КСОРИ Рд, Ра, Имм логоички КСОР са непосредним |

Рд = Ра ^ сигнЕктенд32 (Имм) |

| АНДНИ Рд, Ра, Имм Логично А НЕ са тренутним |

Рд = Ра & (сигнЕктенд32 (Имм)) |

Инструкције огранка- Безусловно

Измените регистар програмског бројача

| БРИД Имм гранати одмах са тренутним одлагањем |

ПЦ = ПЦ+ сигнЕктенд32 (Имм) дозволи извршавање слота за одлагање |

| БРЛИД Рд, Имм гранање и веза одмах са тренутним одлагањем (позив функције) |

Рд = ПЦ ПЦ = ПЦ+& сигнЕктенд32 (Имм) дозволи извршавање слота за одлагање |

| РТСД Ра, Имм повратак из потпрограма |

ПЦ = Ра + сигнЕктенд32 (Имм) дозволи извршавање слота за одлагање |

| РТИД Ра, Имм повратак из прекида |

ПЦ = Ра + сигнЕктенд32 (Имм) дозволи извршавање слота за одлагање подесите прекид прекида у МСР |

Инструкције огранка- Безусловно1

Промените регистар бројача програма када је услов задовољен

| БЕКИ Ра, Имм грана ако је једнака |

ПЦ = ПЦ+ сигнЕктенд32 (Имм) Ако је Ра = = 0 |

| МАСХ Ра, Имм грана ако није једнака |

Рд = ПЦ ПЦ = ПЦ+& сигнЕктенд32 (Имм) Ако Ра! = 0 |

Упутства о подружници- Безусловно2

Промените регистар бројача програма када је услов задовољен

| БЛТИ Ра, Имм грана ако је нижа од |

ПЦ = ПЦ+ сигнЕктенд32 (Имм) Ако је Ра < 0 |

| БЛЕИ Ра, Имм грана ако је нижа једнака од |

Рд = ПЦ ПЦ = ПЦ+& сигнЕктенд32 (Имм) Ако је Ра!< = 0 |

| БГТИ Ра, Имм грана ако је већа од |

ПЦ = ПЦ+ сигнЕктенд32 (Имм) Ако је Ра!> 0 |

| БГЕИ Ра, Имм грана ако је већа једнака од |

ПЦ = ПЦ+сигнЕктенд32 (Имм) Ако је Ра!>= 0 |

Упутства за пуњење/складиштење - Тип А

| ЛВ Рд, Ра, Рб Учитај реч |

Адреса = Ра+Рб Рд = *Адреса |

| СВ Рд, Ра, Рб Чувајте реч |

Адреса – Ра+Рб *Адреса = Рд |

Тип Б

| ЛВИ Рд, Ра, Имн Одмах учитајте реч |

Адреса = Ра + сигнЕктенд32 (Имм) Рд = *Адреса |

| СВ Рд, Ра, Имм Чувајте реч одмах |

Адреса = Ра + сигнЕктенд32 (Имм) *Адреса = Рд |

Остала упутства

| ИММ, Имм непосредан |

Проширите Имм претходне инструкције типа Б на 32-бита. |

| МФС Рд, Са Прелазак из регистра посебне намене |

Рд = Са Са- регистар посебне намене, изворни операнд

|

| МТС Сд, Ра Пређите у регистар посебне намене |

Сд = Ра Сд – регистар посебне намене, одредишни операнд |

Регистри

Архитектура МицроБлазе процесора је потпуно ортогонална и укључује 32-битне регистре опште намене и 32-битне регистре посебне намене као што су програмски бројач и регистар статуса машине.

Архитектура цевовода

МицроБлазе користи 3-степену архитектуру цевовода укључујући дохват, декодирање и комплетне фазе. Аутоматски, прослеђивање података, гране и застој цевовода се одређују унутар хардвера.

Учитај или сачувај архитектуру

МицроБлазе подржава меморију у три величине података: 8 бита (бајт), 16 бита (полуговор) и 32 бита (реч). Дакле, приступи меморији су увек усклађени са величином података. Ово је Биг-Ендиан процесор који користи адресу Биг-Ендиан адресе као и конвенције означавања након приступа меморији.

Прекида

Једном када дође до прекида, онда ће овај процесор завршити садашње извршење да би управљао захтевом за прекид кроз гранање на адресу вектора прекида и чува адресу инструкције која треба да се изврши. Овај процесор ће зауставити будуће прекиде брисањем ИЕ (Интеррупт Енабле) заставице унутар МСР (Мацхине Статус Регистер).

Како ради Мицроблазе?

МицроБлазе процесор подржава 32-битну ширину магистрале и ово језгро процесора је РИСЦ базиран механизам који укључује регистарску датотеку засновану на 32-битном ЛУТ РАМ-у кроз одвојена упутства за приступ меморији и подацима.

Овај процесор једноставно подржава и БлоцкРАМ на чипу и спољну меморију. Слично ИБМ ПоверПЦ-у; сви периферни уређаји користе сличну ЦореЦоннецт ОПБ магистралу; периферне јединице процесора су добро усклађене са ПоверПЦ-ом на Виртек-ИИ Про.

МицроБлазе процесор пружа потпуну флексибилност у одабиру комбинације меморијских, периферних и интерфејс карактеристика које ће вам пружити прецизан систем који вам је потребан на једном ФПГА уз мање трошкове.

Разлика Б/В Мицроблазе вс Рисц-В

Тхе разлика између МицроБлазе и РИСЦ в укључи следеће.

|

Мицроблазе |

Рисц-В |

| То је меко језгро микропроцесора углавном дизајнирано за Ксилинк ФПГА.

|

РИСЦ-В је архитектура скупа инструкција заснована на РИСЦ принципима.

|

| Користи Харвард РИСЦ архитектуру. | Користи архитектуру скупа инструкција. |

| Његова лиценца је власничка (Ксилинк) | Његова лиценца је отвореног кода. |

| Дубина цевовода је 3 или 5. | Дубина цевовода је 5. |

| Његове перформансе су 280 ДМИП. | Његове перформансе су 250 ДМИП. |

| Његова брзина је 235 МХз. | Његова брзина је 250 МХз. |

| Има 1027 ЛУТ-ова. | Има 4125 ЛУТ-ова. |

| Имплементација коришћене технологије је Ксилинк ФПГА. | Имплементација коришћене технологије је ФПГА/АСИЦ. |

Мицроблазе Предности

Тхе предности МицроБлазе-а укључи следеће.

- То је економично.

- Веома је подесив.

- Његове перформансе су високе у поређењу са АРМ-ом.

- Подржан је уграђеним развојним комплетом.

- То је мекана микропроцесор језгро.

- Да би вам помогао да брзо уредите своју апликацију, овај процесор укључује три фиксне конфигурације које се односе на добро познате класе процесора микроконтролер, реал-тиме и процесор апликације.

Мицроблазе апликације

Тхе апликације МицроБлазе укључи следеће.

- Овај процесор испуњава многе различите захтеве апликација као што су индустријске, аутомобилске, медицинске и потрошачке, итд.

- Примене МицроБлазе-а се крећу од једноставних државних машина заснованих на софтверу до сложених контролера који се користе у уграђеним апликацијама или уређајима заснованим на Интернету.

- Оптимизован је за уграђене апликације као што су индустријска контрола, канцеларијска аутоматизација и аутомобилска индустрија.

- МицроБлазе је способан да комуницира са великим скупом периферних уређаја како би се уклопио у апликације средњег обима.

- Мека природа овог процесора чини га прилагодљивим за различите апликације где дизајнери могу да размењују карактеристике за величину како би испунили циљеве у погледу цене и перформанси за медицинске, аутомобилске, индустријске и безбедносне апликације.

Дакле, ради се о томе преглед Мицроблазе процесор. Ово је потпуно опремљено, 32-битно програмабилно РИСЦ меко језгро процесора. Овај процесор испуњава различите захтеве у различитим областима као што су потрошачка, медицинска, индустријска, аутомобилска и тржишта комуникационе инфраструктуре. Изузетно је конфигурабилан, па се користи као уграђени процесор или микроконтролер унутар ФПГА, иначе као копроцесор за АРМ. Ево питања за вас, шта је ФПГА?