Повећавање брзине извршавања програма последично повећава брзину програма процесор. Постоји много начина на који је измишљена хардверска имплементација и софтверска архитектура како би се повећала брзина извршавања. Примећено је да се истовременим извршавањем упутстава може смањити време потребно за извршење. Концепт паралелизма у програмирање је предложен. Према томе, више циклуса може се извршити по такту. Овај концепт програмер може практиковати кроз разне технике као што су Цевоводи, више извршних јединица и више језгара . Међу свим овим методама паралелизма, цевовод се најчешће практикује. Па како се инструкција може извршити методом цевовода? Како то повећава брзину извршења?

Шта је цевовод?

Да бисмо схватили концепт цевовода, погледајмо основни ниво извршавања програма. Упута је најмањи извршни пакет програма. Свака инструкција садржи једну или више операција. Једноставни скаларни процесори извршавају једну или више инструкција по такту, при чему свака инструкција садржи само једну операцију. Упутства се извршавају као редослед фаза како би се постигли очекивани резултати. Овај редослед је дат у наставку

Редослед извршавања упутстава

- ИФ: Преузима упутство у регистар упутстава.

- ИД: Инструцтион Децоде, декодира упутства за опцоде.

- АГ: Генератор адреса, генерише адресу.

- ДФ: Дохватање података, преузима операнде у регистар података.

- ЕКС: Извршење, извршава наведену операцију.

- ВБ: Напиши натраг, упиши резултат на регистар.

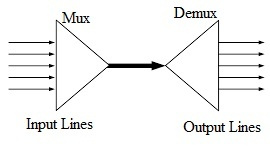

Нису сва упутства потребна за све горње кораке, али већина захтева. Ови кораци користе различите хардверске функције. У цевоводу се ове различите фазе изводе истовремено. У цевоводу се ове фазе сматрају неовисним између различитих операција и могу се преклапати. Дакле, више операција може се изводити истовремено, при чему је свака операција у својој независној фази.

Упутство за цевовод

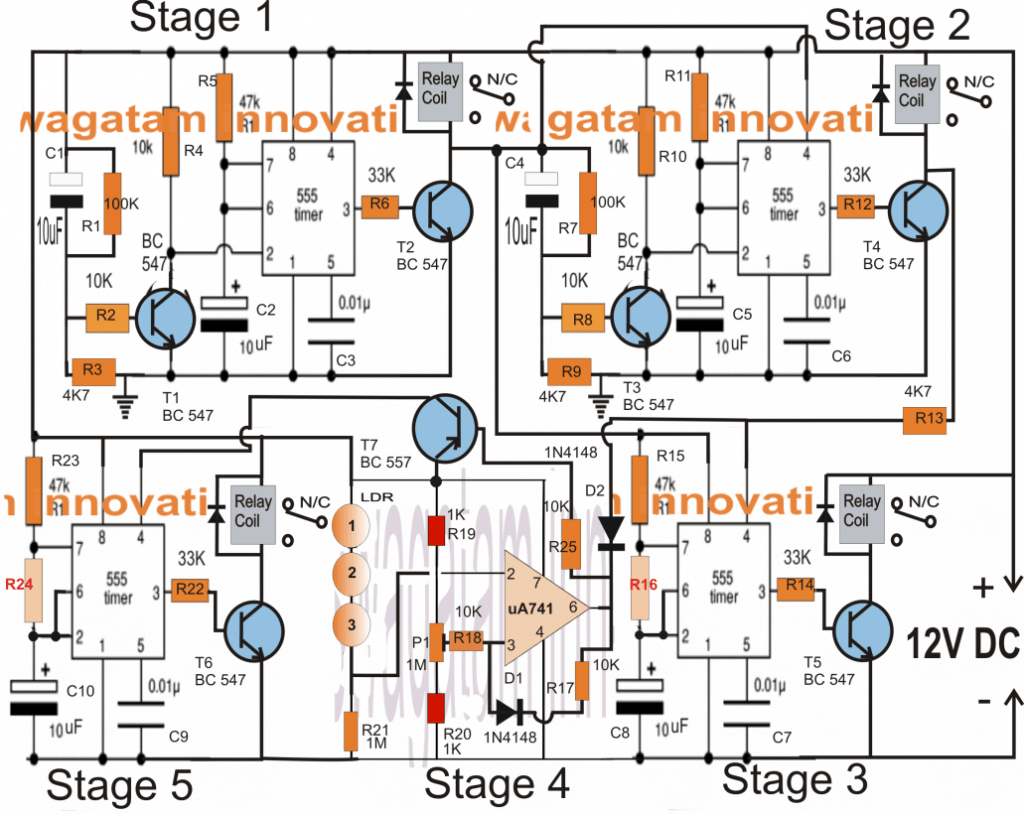

Погледајмо начин обраде упутстава у цевоводу. То се лако може разумети на доњем дијаграму.

Упутство за цевовод

Претпоставимо да су упутства независна. У једноставном процесору цевовода, у датом тренутку, постоји само једна операција у свакој фази. Почетна фаза је ИФ фаза. Дакле, у првом такту се преузима једна операција. Када стигне следећи импулс такта, прва операција прелази у фазу ИД, остављајући ИФ фазу празном. Сада се ова празна фаза додељује следећој операцији. Дакле, током другог импулса такта прва операција је у фази ИД, а друга операција је у фази ИФ.

За трећи циклус, прва операција ће бити у АГ фази, друга операција ће бити у фази ИД, а трећа операција ће бити у фази ИФ. На овај начин, инструкције се извршавају истовремено и након шест циклуса процесор ће издати потпуно извршену инструкцију по такту.

Да ли се ова инструкција извршава секвенцијално, у почетку прва инструкција мора проћи све фазе, а затим би се преузела следећа инструкција? Дакле, за извршење сваке инструкције, процесору би требало шест циклуса такта. Али у процесору који се изводи у цевоводу, јер се извршавање инструкција одвија истовремено, само почетна инструкција захтева шест циклуса, а све преостале инструкције се извршавају по један у сваком циклусу чиме се смањује време извршавања и повећава брзина процесора.

Цевоводна архитектура

Паралелизам се може постићи хардверским, компајлером и софтверским техникама. Да би се искористио концепт цевовода у архитектура рачунара многе процесорске јединице су међусобно повезане и функционишу истовремено. У структурираној процесорској архитектури постоје одвојене процесорске јединице предвиђене за целобројне бројеве и упутства са покретним зарезом. Док је у секвенцијалној архитектури предвиђена једна функционална целина.

Цевоводна процесорска јединица

У статичком цевоводу, процесор треба да проследи инструкцију кроз све фазе цевовода, без обзира на захтев инструкције. У динамичком процесору цевовода, инструкција може заобићи фазе у зависности од својих захтева, али се мора кретати секвенцијалним редоследом. У сложеном динамичком процесору цевовода, инструкција може заобићи фазе, као и одабрати фазе ван реда.

Цевоводи у РИСЦ процесорима

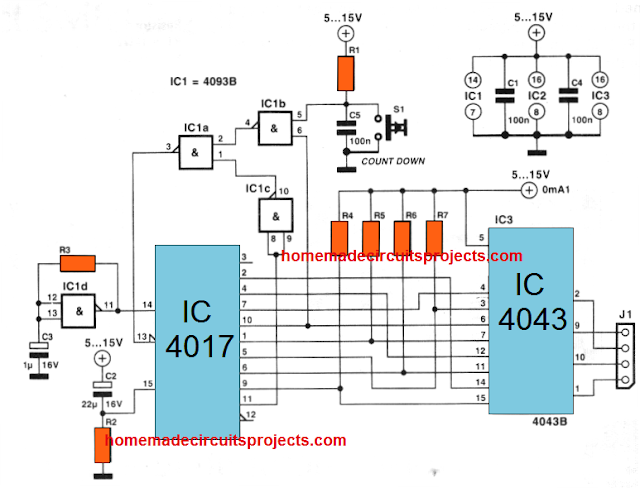

Најпопуларнији РИСЦ архитектура АРМ процесор прати трофазни и петостепени цевовод. У трофазном цевоводу фазе су: Дохвати, Декодирај и Изврши. Овај цевовод има кашњење у 3 циклуса, јер су за појединачна упутства потребна 3 циклуса такта.

АРМ 3 етапе Цевоводи

За правилну имплементацију цевовода хардверску архитектуру такође треба надоградити. Хардвер за тростепени цевовод укључује регистарску банку, АЛУ, преклопник барела, генератор адреса, инкрементер, декодер упутстава и регистре података.

АРМ 3 Стаза цевовода за пренос података

У 5 фаза, фазе цевовода су: Дохваћање, Декодирање, Извршење, Умеђај / подаци и Назад.

Ризичне опасности

У типичном рачунарском програму, поред једноставних упутстава, постоје упутства за гране, операције прекида, упутства за читање и писање. Цевоводи нису погодни за све врсте упутстава. Када се нека упутства изврше у цевоводу, они могу зауставити цевовод или га потпуно испрати. Ова врста проблема насталих током цевовода назива се опасност од цевовода.

У већини рачунарских програма резултат једне инструкције се користи као операнд друге инструкције. Када се такве инструкције извршавају у цјевоводу, долази до рашчлањивања јер резултат прве инструкције није доступан када инструкција два започне сакупљати операнде. Дакле, друга инструкција мора да застане док се не изврши прва и генерише резултат. Ова врста опасности назива се Реад –афтер-врите пипелининг хазард.

Читај после писања опасности од пипе

Извршење упутстава за огранке такође узрокује опасност од цевовода. Упутства огранка док су извршена у цјевоводу утиче на фазе преузимања следећих упутстава.

Понашање понашања у огранку

Предности цевовода

- Повећава се проток инструкција.

- Повећање броја степени цевовода повећава број истовремено извршених инструкција.

- Бржи АЛУ се може дизајнирати када се користи цевовод.

- Пипелинед ЦПУ ради на вишим фреквенцијама такта од РАМ-а.

- Цјевовођење повећава укупне перформансе ЦПУ-а.

Мане цевовода

- Дизајнирање цевоводног процесора је сложено.

- Повећава се кашњење инструкција у цевоводним процесорима.

- Пропусност проточног процесора је тешко предвидети.

- Што је дужи цевовод, то је гори ризик од опасности за упутства за гране.

Увођење цевовода користи сва упутства која следе сличан редослед корака за извршење. Процесоре који имају сложене инструкције, где се свака инструкција понаша другачије од осталих, тешко је применити. Прерађивачи имају разумне уређаје са 3 или 5 степени цевовода, јер се повећањем дубине цевовода повећавају и опасности повезане с њим. Наведите неке од цевоводних процесора са фазом њиховог цевовода?