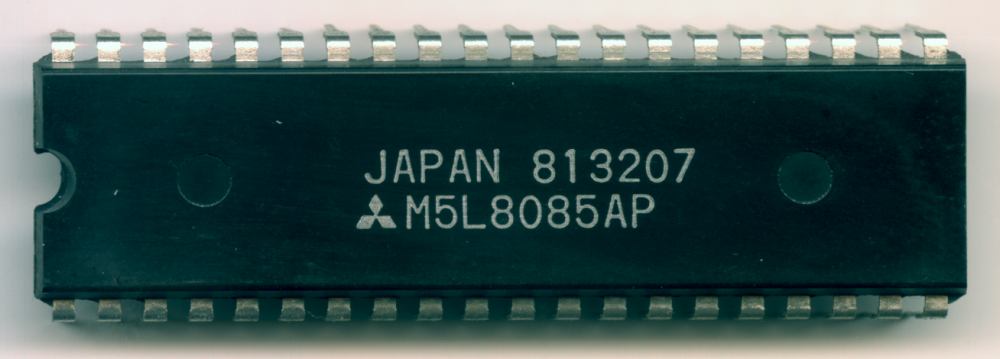

Термин ВЛСИ означава „Технологију интеграције веома великих размера“ која укључује пројектовање интегрисаних кола (ИЦ) комбиновањем хиљада транзистори логично у један чип од различита логичка кола . Ови ИЦ на крају смањују заузети простор кола у поређењу са круговима са конвенционалним ИЦ. Рачунска снага и искоришћење простора главни су изазови ВЛСИ дизајна. Имплементација ВЛСИ пројеката отвара изазовну и светлу каријеру како студентима, тако и истраживачима. Нека од нових трендовских подручја ВЛСИ су Поље програмабилни низ врата апликације (ФПГА), АСИЦ дизајни и СОЦ. Списак неких од ВЛСИ пројеката дат је у наставку за оне студенте који усрдно траже пројекте у овој области. Овај чланак говори о прегледу ВЛСИ пројеката заснованих на ФПГА, Ксилинк, ИЕЕЕ, Мини, Матлаб, итд. Ови пројекти су веома корисни за студенте инжењерства, студенте М.тех.

ВЛСИ пројекти за студенте инжењерства

ВЛСИ пројекти са апстрактима за студенте електроничког инжењерства разматрани су у наставку.

ВЛСИ пројекти

1). Трансформација дискретног таласа заснована на 3Д лифтингу

Овај пројекат помаже у пружању високо прецизних слика коришћењем кодирања слике без губитка података. Да би се то постигло, овај процес примењује филтер за подизање у зависности од трансформације 3Д дискретне таласасте ВЛСИ архитектуре.

2). Дизајнирање СФК мултипликатора са 4-битним уз ефикасан хардвер велике брзине

Овај пројекат се углавном користи за примену модификованог кодера кабине (МБЕ) са 4-битним СФК-ом множилац . Овај мултипликатор пружа добре перформансе у поређењу са конвенционалним кодером кабине. Овај пројекат се углавном користи у апликацијама критичног кашњења.

3). Процесор криптографије који се користи у паметним картицама са ефикасном површином

Овај пројекат се користи за примену три криптографска алгоритма подржана и приватним и јавним кључевима који се користе у Смарт картица апликације за пружање изузетно сигурне верификације и података корисника комуникација .

4). Множилац велике брзине или мале снаге са лажним методом пригушивања напајања

Овај предложени систем филтрира бескорисне лажне сигнале аритметичких јединица како би се избегао непотребан пренос података који не утиче на последње рачунске резултате. Овај систем користи СПСТ метод за мултипликаторе да би постигао пренос података мале снаге и велике брзине.

5). Компресија и декомпресија алгоритма података без губитака

Овај пројекат се углавном примењује за двостепену хардверску архитектуру у зависности од функције алгоритма ПДЛЗВ (Параллел Дицтионари ЛЗВ), као и алгоритма Адаптиве Хуффман типа који се користи за обе примене компресије података без губитака и декомпресије без губитака.

6). Архитектура турбо декодера са ниском комплексношћу за енергетски ефикасне ВСН-ове

Предложени систем се користи за смањење укупне потрошње енергије током преноса података ВСН-ова кроз алгоритам разлагања ЛУТ-Лог-БЦЈР на основне операције АЦС (Адд Цомпаре Селецт).

7). ВЛСИ архитектура за ефикасно уклањање импулсног шума са слике

Овај предложени систем углавном се користи за визуелно побољшање квалитета слике како би се избегле шансе да буде оштећен импулсним шумом за примену ефикасне ВЛСИ архитектуре уз помоћ филтера за очување ивица.

8). Архитектура процесора у меморији који се користи за компресију мултимедије

Овај предложени систем пружа архитектуру мале сложености за а процесор у меморији за подршку мултимедијалних апликација, наиме компресија слике, видео кроз примену огромних појединачних упутстава, више концепата података и реч упутства.

9). Техника синхронизације времена са брзином симбола за бежичне ОФДМ системе мале снаге

Овај предложени систем углавном се користи за побољшање деловања бежичног ОФДМ-а (Ортогонал Фрекуенци Дивисион Мултиплексирање ) систем кроз смањење снаге читавог основног опсега уз помоћ сата генератор са фазно подесивим и динамичким контролером за одређивање времена узорковања.

10). Имплементација мултипликатора мале снаге и велике брзине заснована на акумулатору са СПСТ аддером и верилогом

Овај пројекат се користи за дизајнирање МАЦ мале снаге и велике брзине (мултипликатор и акумулатор) прихватањем методе лажног потискивања снаге на МБЕ (модификовани кодер кабине). Коришћењем овог дизајна може се избећи расипање снаге целог прекидача.

11). Дизајн и примена роботског процесора омогућавањем спречавања судара са РФИД технологијом

Предложени систем се углавном користи за имплементацију роботског процесора са системом за спречавање судара како би се избегао физички судар робота у окружењу више робота. Овај алгоритам се углавном примењује помоћу ВХДЛ и РФИД технологије.

12). Пројектовање логичког кола са енергетски ефикасним коришћењем адијабатске методе

Овај систем ефикасно приказује дизајн логичког кола адијабатском методом у поређењу путем конвенционалног ЦМОС дизајна уз помоћ кола НАНД & НОР капије . Коришћењем адијабатске методе може се смањити расипање снаге унутар мреже као и рециклирати ускладиштену енергију унутар кондензатора оптерећења.

3). Систем за шифровање за повећање рачунарске брзине система

Главна намера овог пројекта је да се побољша сигурност преноса података како би се побољшала брзина рачунара применом алгоритма АЕС помоћу ФПГА. Дакле, ова симулација, као и математички дизајн, могу се извршити уз помоћ ВХДЛ кода.

14). ИП блок АХМ или напредне магистрале високих перформанси

Овај пројекат се углавном користи за дизајн напредне архитектуре Микроконтролер Сабирница (АМБ) помоћу АХБН (напредна магистрала високих перформанси). Овај пројекат се може дизајнирати са ВХДЛ кодом применом блокова попут мастер & саве.

15). Мултимоде РФ примопредајник заснован на ДСМ-у са вишеканалним

Овај систем се углавном користи за дизајнирање вишемодне архитектуре предајника и пријемника и РФ вишеканалног модула са Делта-Сигма модулом. Овај предложени систем користи ВХДЛ језик за примену две архитектуре.

16). Концентратор нокаут прекидача помоћу асинхроног режима преноса

Коришћењем овог пројекта може се дизајнирати нокаут прекидач заснован на асинхроном преносу уз помоћ алата попут ВХС и ВХДЛ. Овај прекидач за искључење може се користити у мрежама виртуелних пакетних кола, као и у апликацијама датаграма.

17). Понашање синтезе асинхроних кола

Овај пројекат се углавном користи за пружање технике бихевиоралне синтезе која се користи за асинхроне кругове. Оба предлошка попут балсе и асинхроне имплементације су главни елементи у дизајну.

18). АМБА дизајн помоћу компатибилног меморијског контролера АХБ

Овај пројекат се користи за дизајнирање МЦ (меморијског контролера) у зависности од АМБА (Напредна архитектура сабирнице микроконтролера) за контролу системске меморије помоћу главне меморије попут СРАМ-а и РОМ-а.

19). Имплементација Царри Трее Аддер

Носачи стабала засновани на ВЛСИ дизајну називају се најбољим збрајачима за разлику од уобичајених бинарних сабирача. Додавачи који су имплементирани овим пројектом су растуће дрво, когге-камен и оскудни когге-камен.

20). ЦОРДИЦ ротација фиксног угла заснована на дизајну

Главни концепт овог предложеног система је окретање вектора помоћу фиксних углова. Ови углови су неопходни за игре, роботику, обрађиванње слике итд. Коришћењем овог пројекта векторска ротација се може постићи коришћењем специфичних углова дизајном ЦОРДИЦ (дигитални рачунар са координатном ротацијом).

21). Дизајн ФИР филтера са дистрибуираном аритметиком тражилице

Овај предложени систем углавном побољшава ФИР филтер перформансе пројектовањем помоћу дистрибуиране аритметике тродимензионалне табеле претраживања уместо множитеља. Дакле, овај дизајн се може применити помоћу софтвера попут ФПГА и Ксилинк.

22). Пусх-Пулл импулсне резе са условом велике брзине и мале снаге

Овај пројекат се користи за извођење енергетски ефикасних и импулсних реза високих перформанси које се углавном користе за ВЛСИ системе коришћењем нове топологије. Будући да ова топологија углавном зависи од завршне фазе пусх-пулл-а која се користи помоћу две подељене траке кроз условни генератор импулса.

23). Аритметички кодер ВЛСИ архитектура у СПИХТ-у

Овај предложени систем побољшава проток методе аритметичког кодирања у скупу партиција у компресији слике хијерархијског стабла (СПИХТ) брзом архитектуром у зависности од ФПГА.

24). Сузбијање буке ЕКГ сигнала на основу ФПГА

Овај пројекат се користи за задржавање шума унутар ЕКГ сигнала кроз два средња филтера са 91 и 7 величина тачака узорка. Дакле, овај процес се може постићи применом ФПГА дизајн на основу ВХДЛ кода.

25). ВЛСИ процесор за скалирање слика високих перформанси са ниском ценом

Овај пројекат се користи за примену алгоритма за процесор за скалирање слика заснован на ВЛСИ са мање меморије и високим перформансама. Предложени дизајн система углавном садржи комбиновање филтера, реконфигурабилне динамичке методе и дељење хардвера ради смањења трошкова.

26). Архитектура систоличког низа Дизајн и ефикасна примена

Главни концепт овог пројекта је дизајнирање хардверског модела који се користи за мултипликатор систолног низа. Овај низ се углавном може користити за извршавање бинарног множења уз помоћ ВХДЛ платформе. Предложени дизајн система може се применити помоћу софтвера ФПГА и Исим.

27). КПСК дизајн и синтеза помоћу ВХДЛ кода

КПСК је једна од главних метода модулације. Ова метода се користи у апликацијама сателитског радија. Ова техника модулације може се применити кроз реверзибилне логичке капије. Дизајн КПСК технике може се извршити уз помоћ ВХДЛ кода.

28). Дизајн и примена ДДР СДРАМ контролера великом брзином

Предложени систем користи се за дизајн ДДР СДРАМ контролера за пренос рафалних података у зависности од велике брзине за синхронизацију ових података између кола уграђеног система и ДДР СДРАМ-а. Коришћењем језика ВХДЛ, код се може развити.

29). 32-битни дизајн и имплементација РИСЦ процесора

Главни концепт овог пројекта је примена 32 бита РИСЦ (рачунар са смањеним упутством) уз помоћ алата попут КСИЛИНК ВИРТЕКС4. У овом пројекту је дизајнирано 16 скупова инструкција где год се свака инструкција може извршити у једном ЦЛК циклусу помоћу петофазне методе цевовода.

30). Имплементација аутобусног моста између АХБ и ОЦП

Предложени систем користи се за пројектовање сабирничког моста између два протокола, наиме заједнички и стандардни. Веома су популарни комуникацијски протоколи попут АХБ (напредна магистрала високих перформанси) и ОЦП (протокол отвореног језгра) који се користе у апликацијама СоЦ (систем на чипу) .

Идеје за ВЛСИ пројекте за студенте инжењерства

Списак ВЛСИ пројеката заснованих на ФПГА, МатЛаб, ИЕЕЕ и Мини пројектима за студенте инжењерства наведен је у наставку.

ВЛСИ пројекти за студенте М. Тецх

Списак ВЛСИ пројеката заснованих на М. Тецх Студент укључује следеће.

- Просторно ефикасан и изузетно поуздан РХБД заснован И0Т меморијски ћелијски дизајн који се користи у ваздухопловним апликацијама

- Фазни детектор са више нивоа у пола стопе који се користи за ЦЛК и кругове за опоравак података

- Компаратор са малом снагом и великом брзином који се користи за прецизне примене

- Преносник нивоа напона са интегрисаним мултиплексером високих перформанси

- Тернарни сабирач заснован на ЦНТФЕТ-у, високих перформанси

- Дизајн упоредника магнитуде са малом снагом

- Дизајн прага логичке капије са тренутним режимом за анализу кашњења

- Мешани логички декодери дизајнирају са малом снагом и високим перформансама

- Слееп Цонвентион Логиц Тестабилити Десигн

- Пребацивач нивоа напона за апликације са двоструким напајањем са великом брзином и ефикасношћу напајања

- Дизајн и анализа двостраних компаратора мале снаге и ниског напона

- Дизајн флип-флоп заснован на импулсно окидачу са малом снагом помоћу методе проласка сигнала

- Дизајн ефикасних кругова заснован на ФЕТ-овима који се могу конфигурисати током извођења

- Дизајн упоредника магнитуде са малом снагом

- Анализа кашњења дизајна логичких врата са прагом тренутног режима

Тхе ВЛСИ пројекти засновани на ФПГА за студенте инжењерских наука и ЦМОС ВЛСИ дизајнира мини-пројекте наведени су у наставку.

- Дизајн и карактеризација каљених кругова СЕУ за ФПГА на основу СРАМ-а

- Компактни ЦМОС хибридни ЛУТ дизајн и потенцијална апликација засновани на Мемристору који се користи у ФПГА

- Примена ФПГА за мерење даљине заснована на ултразвучном сензору

- Примена ФПГА за мултипликатор кабине са Спартан6 ФПГА

- Дискретна таласна трансформација заснована на подизању помоћу Спартан3 ФПГА

- АРМ контролер у роботици који користи ФПГА

- УАРТ заснован на ФПГА са вишеканалним

- Сузбијање ЕКГ шумова помоћу ФПГА

- Имплементација ФПГА заснована на УТМИ-у и слој протокола УСБ 2.0

- Примена медијанског филтера са Спартан3 ФПГА

- Имплементација ФПГА заснована на алгоритму АЕС

- Систем упозорења заснован на ПИЦ-у за примену ФПГА са Спартан 3ан-ом

- Имплементација ФПГА за дизајн контролера за системе даљинског очитавања

- Комплет за обраду слике ФПГА користећи филтрирање слике линеарним и морфолошким

- Имплементација медицинске фузије слике засноване на Спартан3 ФПГА

Списак ВЛСИ мини пројекти који користе ВХДЛ код укључује следеће.

- Компаратор са великом брзином користећи ВЛСИ

- Множитељ плутајуће тачке користећи ВЛСИ

- Конверзија бинарног у сиво засновано на ВЛСИ

- Дигитални филтер

- ЦЛК Гатинг заснован на ВЛСИ

- Ведски мултипликатор

- ЦМОС ФФ користећи ВЛСИ

- Архитектура паралелног процесора који користи ВЛСИ

- Фулл Аддер заснован на ВЛСИ-у

- Дизајн ДРАМ / динамичке меморије са случајним приступом заснован на ВЛСИ

- Изглед СРАМ заснован на ВЛСИ

- ВЛСИ процесор за дигитални сигнал

- Мултиплекер заснован на ВЛСИ-у

- Дизајн МАЦ јединице засноване на ВЛСИ

- Диференцијатор заснован на ВЛСИ-у

- ФФТ заснована на ВЛСИ или брза Фуријеова трансформација

- Архитектура дискретне косинусне трансформације засноване на ВЛСИ

- Дизајн 16-битног мултипликатора помоћу ВЛСИ19

- ВЛСИ дизајнирање ФИФО пуфера

- Брзи акцелератор заснован на ВЛСИ

ВЛСИ пројекти који користе МАТЛАБ и Ксилинк

Списак ВЛСИ пројеката заснованих на МАТЛАБ-у и ВЛСИ пројектима који користе Ксилинк укључује следеће.

- Дизајн и анализа ЦДМА модема са МАТЛАБ-ом

- Дизајн ФИР филтера помоћу ВХДЛ-а на ФПГА и МАТЛАБ анализи

- МоделСим & Матлаб или Симулинк симулација система за аутомобилско инжењерство

- Додавачи засновани на Ксилинк-у попут Риппле Царри & Царри Скип

- Аритметичка јединица заснована на 32-битној покретној тачки

- АЛУ заснован на покретној тачки

- РИСЦ процесор заснован на 32-битном

- Конволуционе могућности ортогоналног кода

- Аутомати засновани на Ксилинку и Верилогу

- Паралелни додавачи префикса засновани на Ксилинк-у са 256-битним

- Протокол за узајамну потврду идентитета помоћу Ксилинка

- Приступна структура са једноструким циклусом за логички тест користећи Ксилинк

- УТМИ и протокол УСБ2.0 заснован на слоју користећи Ксилинк

- Конфигурација компресије и декомпресије података помоћу Ксилинк ФПГА

- ФПГА засновани на БИСТ и Спартан серији засновани на Ксилинк 4000

- ИИР филтер заснован на МАТЛАБ & ВЛСИ

- ФИР филтер помоћу МАТЛАБ-а

ИЕЕЕ пројекти

Тхе списак ИЕЕЕ ВЛСИ пројеката је наведено у наставку.

- ВЛСИ систем бежичне кућне аутоматизације заснован на Блуетоотх-у

- Уклањање импулсног шума унутар слике коришћењем ефикасне архитектуре ВЛСИ

- Архитектура процесора у меморији за мултимедијалну компресију

- Надгледање система температуре помоћу Цлоуд & ИоТ-а

- Имплементација ОФДМ система са ИФФТ и ФФТ

- Дизајн и примена Хамминговог кода са Верилог-ом

- Препознавање отиска прста засновано на ВХДЛ-у помоћу Габор-овог филтера

- Аритметичке функције Мапирање са РОМ-ом у зависности од приступа апроксимације

- Анализа перформанси високе ефикасности и ниске густине декодера за проверу парности у апликацијама мале снаге

- ФФТ архитектуре са повратним напоном цевног радикса-2к

- Дизајн јапанки за ВЛСИ апликације применом ЦМОС технологије са високим перформансама

- Дизајн ФИР филтера са табелом претраживања према дистрибуираној аритметици

- ВЛСИ процесор са ниским трошковима и побољшаним скалирањем слика

- АСИЦ имплементација и дизајн напредног турбо енкодера и декодера са 3ГПП ЛТЕ

- Пусх-Пулл импулсне резе са условом мале снаге и велике брзине

- Побољшано скенирање у тестирању скенирања мале снаге

- Аритметички кодер ВЛСИ архитектура за СПИХТ

- Примена ВХДЛ-а за УАРТ

- ВЛСИ регулатор напона са малим испадањем

- Фласх АДЦ дизајн са побољшаном шемом упоређивача

- Дизајн мултипликатора мале снаге са сложеним стилом логике константног кашњења

- Компаратор са двоструким репом са високим перформансама и малом снагом

- Фласх систем за складиштење са високим перформансама у зависности од међуспремника за писање и виртуелне меморије

- ФФ мале снаге заснован на Слеепи Стацк приступу

- ЛФСР оптимизација напајања за БИСТ мале снаге примењена у ХДЛ-у

- Дизајн и примена аутомата са Верилог ХДЛ-ом

- Дизајн акумулатора заснован на стварању узорка са 3 тежине са ЛП-ЛСФР

- Реед-Соломон декодер велике брзине и мале сложености

- Бржа техника дизајнирања мултипликатора Дадда

- Пријемник ФМ радија на основу дигиталне демодулације

- Генерирање тест узорка са БИСТ шемама

- Имплементација ВЛСИ архитектуре са брзим цевоводом

- Дизајн ОЦП протокола сабирнице на чипу користећи функције сабирнице

- Детектор фазне фреквенције и дизајн пумпе за пуњење који се користе за високофреквентну фазно закључану петљу

- Кеш меморија и дизајн кеш контролера са ВХДЛ-ом

- Имплементација компресора за сабијање мале снаге 3-2 и 4-2 заснована на АСТРАНИ

- Систем за обрачун претплаћене електричне енергије помоћу дизајна на чипу

- Имплементација преклапања помоћу логичке ћелије и њене анализе снаге

- Носите поглед напред са различитим анализама перформанси битова помоћу ВХДЛ-а

- Дизајн слоја везе података са Ви-Фи МАЦ-ом Протоколи

- Примена ФПГА за протокол узајамне потврде идентитета са модуларном аритметиком

- Генерација ПВМ сигнала помоћу ФПГА и променљивог радног циклуса

Пројекти у реалном времену

Списак ВЛСИ пројекти у реалном времену углавном укључују ВЛСИ мини пројекте који користе ВХДЛ код и ВЛСИ софтверске пројекте за студенте ЕЦЕ инжењерства.

- Прагматична интеграција СРАМ кеша редова у хетерогену тродимензионалну архитектуру ДРАМ-а користећи ТСВ

- Уграђена техника самотестирања за дијагнозу грешака у кашњењу у пољским програмирљивим низовима капија заснованих на кластеру

- АСИЦ Дизајн сложеног множитеља

- Повољна имплементација ВЛСИ за ефикасно уклањање импулсне буке

- Заснован на ФПГА ПВМ свемирског вектора Управљачка ИЦ за трофазни асинхронски погон

- ВЛСИ примена аутоматског корелатора и ЦОРДИЦ алгоритма за ОФДМ заснован ВЛАН

- Аутоматско издвајање пута помоћу сателитских снимака високе резолуције

- ВХДЛ дизајн за сегментацију слика помоћу Габор-овог филтера за откривање болести

- Турбо декодерска архитектура мале сложености за енергетски ефикасне бежичне сензорске мреже

- Побољшање могућности прављења ортогоналних кодова применом ФПГА

- Дизајн и примена плутајуће тачке АЛУ

- ЦОРДИЦ дизајн за фиксни угао ротације

- Производ Реед-Соломон кодови за примену НАНД Фласх контролера на ФПГА чипу

- Статистичко побољшање приноса приступа за читање СРАМ-а коришћењем кругова негативног капацитета

- Управљање напајањем МИМО мрежних интерфејса на мобилним системима

- Дизајн стандарда за шифровање података за шифровање података

- Аддер мале снаге и површине за ефикасно ношење

- Синтеза и примена УАРТ-а помоћу ВХДЛ кодова

- Побољшане архитектуре за јединицу сабирног сабирања са плутајућом тачком

- 1-битни потпуно дигитални предајник заснован на ФПГА који користи Делта-Сигма модулацију са РФ излазом за СДР

- Оптимизација употребе ланчане претраге у БЦХ декодеру за пренос брзине грешака

- Дигитални дизајн ДС-ЦДМА предајника који користи Верилог ХДЛ и ФПГА

- Дизајн и примена ефикасне архитектуре систоличког низа

- Алгоритам учења динамике робота заснован на ВЛСИ-у

- Свестрани дизајн мултимедијалних функционалних јединица користећи лажну технику пригушивања напајања

- Дизајн аутобуског моста између АХБ и ОЦП

- Бехевиорална синтеза асинхроних кола

- Оптимизација брзине модификованог Витерби декодера заснованог на ФПГА

- Имплементација И2Ц интерфејса

- Множилац велике брзине / мале снаге који користи напредну технику лажног потискивања напајања

- Стезање виртуелног напона напајања струјних кругова за активно смањење цурења и поузданост оксида у затварачу

- ФПГА заснован на енергетски ефикасном каналу за софтвер дефинисан радиом

- ВЛСИ архитектура и ФПГА прототипирање дигиталног фотоапарата за заштиту и аутентификацију слике

- Операција Побољшање унутрашњег робота

- Дизајн и примена ОН-Цхип пермутационе мреже за вишепроцесорски систем-он-Цхип

- Метод синхронизације временске брзине преноса симбола за бежичне ОФДМ системе мале снаге

- ДМА контролер (директан приступ меморији) помоћу ВХДЛ / ВЛСИ

- Реконфигурабилни ФФТ помоћу архитектуре засноване на ЦОРДИЦ-у за МИМИ-ОФДМ пријемнике

- Лажна техника пригушивања напајања за мултимедије / ДСП апликације

- Ефикасност БЦХ кодова у воденим жиговима дигиталних слика

- Двострука брзина преноса података СД-РАМ контролер

- Примена Габор филтра за препознавање отиска прста помоћу Верилог ХДЛ

- Дизајн практичне нанометрске скале вишка преко свесне стандардне ћелијске библиотеке за побољшани вишак преко 1 уметања

- Алгоритам компресије и декомпресије података без губитака и његова хардверска архитектура

- Оквир за исправљање вишебитних софт грешака

- Ефикасна компресија података заснована на Витербију

- Примена ФФТ / ИФФТ блокова за ОФДМ

- Компресија слике заснована на таласима помоћу ВЛСИ прогресивног кодирања

- ВЛСИ примена потпуно пипелираног мултипликатора мање од 2д ДЦТ / ИДЦТ архитектуре за Јпег

- Емулација грешака заснована на ФПГА синхроних секвенцијалних кола

Дакле, ово је све о листи ВЛСИ пројеката за инжењерство, студентима М.Тецх-а који су корисни при одабиру теме последње године пројекта. Након што сте провели драгоцено време док сте пролазили кроз ову листу, верујемо да имате прилично добру идеју да одаберете тему пројекта по свом избору са листе ВЛСИ пројеката и надамо се да имате довољно самопоуздања да преузмете било коју тему из листа. За даље детаље и помоћ у вези са овим пројектима можете нам писати у одељку за коментаре који је дат у наставку. Ево питања за вас, шта је ВХДЛ?

Фото кредит

- ВЛСИ пројекти од сет-тецх