У свакодневном животу наилазимо на разне врсте електронских уређаја. Једна од технологија која је донела револуцију у производњи електронике је „ Интегрално коло “. Ова технологија је смањила величину електронских производа повећавањем густине логичка врата по чипу. Данас имамо различите типове и конфигурације ИЦ-а. Како уочавамо около, откривамо да се неке ИЦ могу користити само за једну одређену апликацију, док се неке ИЦ могу репрограмирати и користити за различите апликације. Ове врсте ИЦ-а називају се АСИЦ-има. Али како се разликују? Како је могуће да их репрограмирате? Зашто се неке ИЦ не могу репрограмирати? Ускочите у проналажење одговора на ова питања.

Шта је АСИЦ (интегрисани круг специфичан за апликацију)?

АСИЦ пуни образац је Интегрисани круг специфичан за апликацију. Ови кругови су специфични за примену, тј. прилагођене ИЦ-ове за одређену примену. Обично су дизајнирани са основног нивоа на основу захтева одређене апликације. Неки од основних примери специфичних интегрисаних кола за специфичне примене су чипови који се користе у играчкама, чипови који се користе за повезивање меморије и микропроцесора итд ... Ови чипови се могу користити само за ону једну апликацију за коју су дизајнирани. Претпоставља се да су ови врсте ИЦ пожељни су само за оне производе који имају велику производњу. Како су АСИЦ дизајнирани од основног нивоа, они имају високу цену и препоручују се само за велике количине производње.

Главна предност АСИЦ-а је смањена величина чипа јер је велики број функционалних јединица кола конструисан преко једног чипа. Савремени АСИЦ углавном укључује 32-битне микропроцесор , меморијски блокови, мрежни кругови итд ... Таква врста АСИЦ-а је позната као Систем на чипу . Развојем производне технологије и повећаним истраживањем метода дизајнирања развијају се АСИЦ-ови са различитим нивоима прилагођавања.

Врсте АСИЦ-а

АСИЦ-ови су категоризовани на основу количине прилагодбе коју програмер сме да уради на чипу.

Врсте АСИЦ-а

Потпуно прилагођени

У овој врсти дизајна све логичке ћелије су прилагођене направљеним за одређену примену, тј. дизајнер мора посебно да направи логичке ћелије за кола. Сви слојеви маске за међусобно повезивање су прилагођени. Дакле, програмер не може да мења међусобне везе чипа и током програмирања мора бити свестан распореда кола.

Један од најбољих примера потпуно прилагођеног АСИЦ-а је микропроцесор. Ова врста прилагођавања омогућава дизајнерима да граде различите аналогне склопове, оптимизоване меморијске ћелије или механичке структуре на једном ИЦ-у. Овај АСИЦ је скуп и врло дуготрајан за производњу и дизајн. Потребно је време за дизајн ових ИЦ око осам недеља.

Они су обично намењени апликацијама високог нивоа. Максималне перформансе, минимализована површина и највиши степен флексибилности главне су одлике потпуно прилагођеног дизајна. На крају, ризик је велик у дизајну, јер се логичке ћелије, отпорници итд.

Полуприлагођени

У овом типу дизајна логичке ћелије су преузете из стандардних библиотека, тј. нису ручно израђени као у Потпуно прилагођеном дизајну. Неке маске су прилагођене, док су неке преузете из унапред дизајниране библиотеке. На основу типа логичких ћелија преузетих из библиотеке и количине прилагођавања дозвољене за међусобне везе, ови АСИЦ-и су подељени у два типа - стандардни АСИЦ заснован на ћелијама и АСИЦ заснован на низу врата.

1). Стандардни АСИЦ заснован на ћелијама

Да бисмо их прво познавали, схватимо шта представља стандардна библиотека ћелија. Неке од логичких ћелија попут И капије, ИЛИ капије , мултиплексери, Папуче су дизајнирани од стране дизајнера користећи различите конфигурације, стандардизовани и похрањени у облику библиотеке. Ова колекција је позната као стандардна ћелијска библиотека.

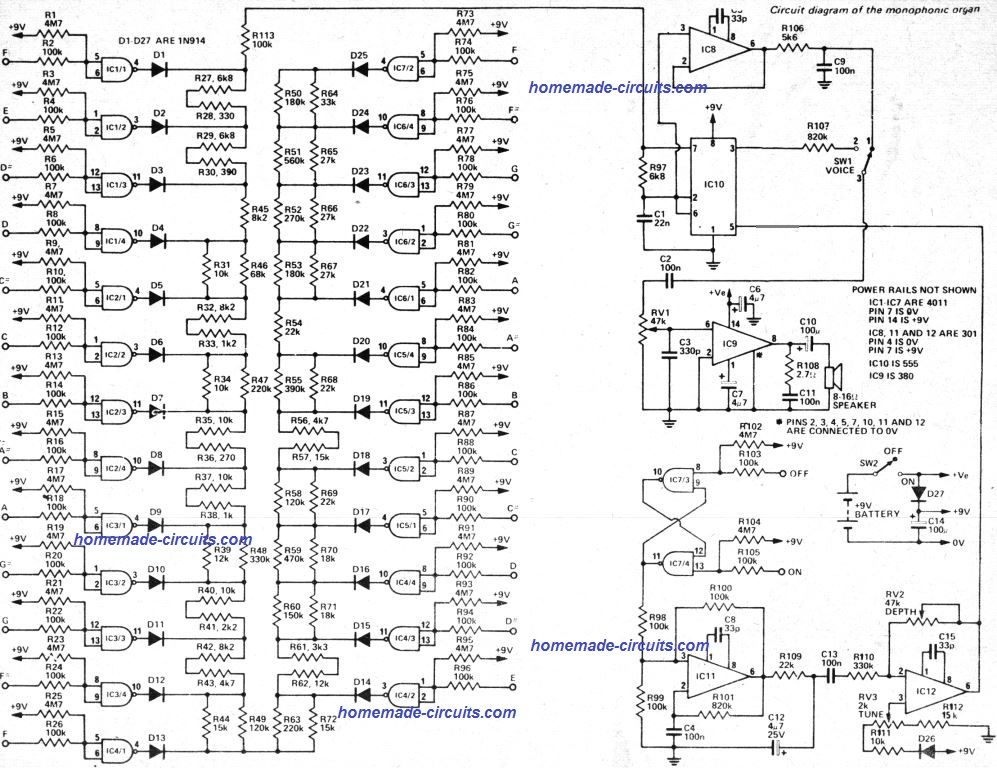

Стандардни АСИЦ заснован на ћелијама

У стандардним ћелијама се користе АСИЦ логичке ћелије из ових стандардних библиотека. На АСИЦ чипу стандардно подручје ћелија или флексибилни блок чине стандардне ћелије поређане у облику редова. Заједно са овим флексибилним блоковима на чипу се користе мега ћелије попут микроконтролера или чак микропроцесора. Ове мега ћелије су познате и као Мега функције, макрони на системском нивоу, фиксни блокови, Функционални стандардни блокови.

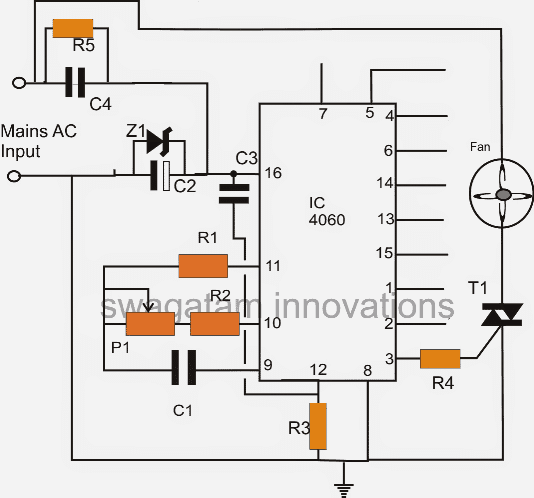

Горња слика представља стандардни АСИЦ ћелије са једном стандардном површином ћелије и четири фиксна блока. Слојеви маски су прилагођени. Овде дизајнер може да постави стандардне ћелије било где на калупу. Они су такође познати као Ц-БИЦ.

2). АСИЦ на основу низа капија

Ова врста полуприлагођених АСИЦ-а је унапред дефинисана транзистори на силицијумовој плочици, тј. дизајнер не може променити постављање транзистора присутних на матрици. Основни низ је предефинисани образац низа врата, а основна ћелија је најмања понављајућа ћелија основног низа.

Дизајнер је одговоран само за промену међусобне везе између транзистора помоћу првих неколико металних слојева матрице. Дизајнер бира из библиотеке низа врата. Они се често називају Маскед Гате Арраи. АСИЦ засновани на низу капија су три врсте. Они су канализовани низови врата, низови канала без канала и структурирани низови врата.

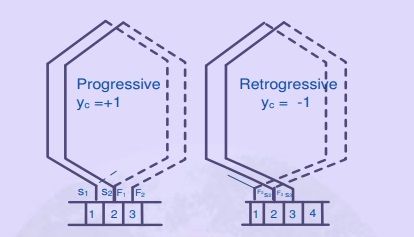

а) .Каналисани низ врата

У овој врсти низа врата, простор за ожичење је остављен између редова транзистора. Они су слични ЦБИЦ-у јер је остављен простор за међусобно повезивање блокова, али у канализованим редовима ћелија низа врата су фиксни по висини, док се у ЦБИЦ-у тај простор може прилагодити.

Канализовани низ врата

Неке од главних карактеристика овог низа врата су: овај низ врата користи унапред дефинисане размаке између редова за међусобно повезивање. Време израде је два дана до две недеље.

б). Низ мањег пролаза за канал

Не остаје слободан простор за усмеравање између редова ћелија као што се види у канализованом низу врата. Овде се усмеравање врши изнад ћелија низа врата, јер можемо прилагодити везу између метала 1 и транзистора. За усмеравање остављамо транзисторе који леже на путу усмеравања неискоришћени. Време израде је око две недеље.

Низ мањег пролаза за канал

ц). Структурни низ врата

Ова врста низа врата има уграђени блок заједно са редовима низа врата као што је приказано горе. Структурирани низ врата има већу површинску ефикасност од ЦБИЦ. Попут маскираног низа врата, они имају ниже трошкове и бржи заокрет. Овде фиксна величина уграђене функције представља ограничење на структурираном низу врата. На пример, да ли овај низ капија садржи подручје резервисано за 32к битни контролер, али ако у апликацији требамо само подручје за 16к битни контролер, преостало подручје се троши. Свих матрица гејтова има време обраде од два дана до две недеље и сви имају прилагођене међусобне везе.

Структурни низ врата

Програмабилни АСИЦ

Постоје две врсте програмабилних АСИЦ-а. То су ПЛД и ФПГА

ПЛД-ови (програмабилни логички уређаји)

То су стандардне ћелије које су лако доступне. ПЛД можемо програмирати да прилагоди део апликације, па се они сматрају АСИЦ-ом. За програмирање ПЛД-а можемо користити различите методе и софтвер. Садрже редовну матрицу логичких ћелија, обично програмабилну логику низа, заједно са јапанкама или резама. Овде су међусобне везе присутне као један велики блок.

ПРОМ је уобичајени пример ове ИЦ. ЕПРОМ користи МОС транзисторе као међусобно повезане, тако да применом високог напона можемо то програмирати. ПЛД-ови немају прилагођене логичке ћелије или међусобно повезивање. Имају брзи дизајн.

Програмабилни логички уређаји

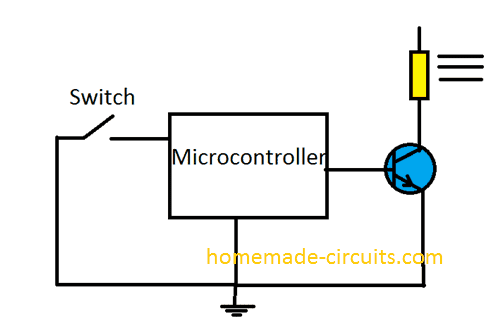

ФПГА (Фиелд Программабле Гате Арраи)

Тамо где ПЛД-ови имају програмабилну логику низа као логичке ћелије ФПГА има распоред врата сличан низу. ПЛД-ови су мањи и мање сложени од ФПГА-а. Због своје флексибилности и карактеристика, ФПГА замењује ТТЛ у микроелектронским системима. Преокрет у дизајну је само неколико сати.

Поље програмабилни низ врата

Језгро се састоји од програмабилних основних логичких ћелија које могу изводити и једно и друго комбинациона и секвенцијална логика . Можемо програмирати логичке ћелије и међусобно се повезивати помоћу неких метода. Основне логичке ћелије окружене су матрицом програмабилних међусобних веза, а језгро окружено програмабилним И / О ћелијама.

ФПГА се обично састоји од подесивих логичких блокова, подесивих И / О блокова, програмабилних међусобних веза, тактних кола, АЛУ, меморије, декодера.

Видели смо различите врсте АСИЦ-а на располагању. Сада да схватимо када се сва ова прилагођавања и међусобне везе извршавају током производње.

Ток дизајна интегрисаног круга (АСИЦ) специфичан за апликацију

Дизајн АСИЦ-а се изводи корак по корак. Овај редослед корака познат је као АСИЦ Дизајн Проток. Кораци дизајнерског тока дати су на доњој табели.

АСИЦ дизајн ток

Улаз за дизајн: У овом кораку микроархитектура дизајна је имплементирана помоћу језика за опис хардвера као што су ВХДЛ, Верилог и Систем Верилог.

Синтеза логике: У овом кораку се помоћу ХДЛ-а припрема мрежна листа логичких ћелија које ће се користити, типови међусобних веза и сви остали делови потребни за апликацију.

Партиционирање система: У овом кораку делимо матрицу велике величине на комаде величине АСИЦ.

Симулација пре распореда: У овом кораку се врши симулациони тест како би се проверило да ли дизајн садржи грешке.

Подно планирање: У овом кораку блокови нетлист-а су распоређени на чипу.

Постављање: У овом кораку се одлучује о локацији ћелија унутар блока.

Рутирање: У овом кораку се повлаче везе између блокова и ћелија. Вађење: У овом кораку одређујемо електрична својства попут вредности отпора и вредности капацитивности интерконекције.

Симулација након распореда: Пре подношења модела за производњу ова симулација се врши да би се проверило да ли систем правилно функционише заједно са оптерећењем међусобног повезивања.

Примери АСИЦ-а

Пошто смо познавали различите карактеристике АСИЦ-а, сада ћемо видети неке примере АСИЦ-а.

Стандардни АСИЦ заснован на ћелијама: ЛЦБ 300к, 500к од ЛСИ Логиц Цомпани, СИГ1, 2, 3 породице од АББ Хафо Инц., ГЦС90К од ГЦС Плессеи.

Производи низа врата: АУА20К компаније Харрис Семицондуцтор, СЦКС6Бкк компаније Натионал Семицондуцторс, породице ТГЦ / ТЕЦ компаније Текас Инструментс.

ПЛД производи: ПАЛ породица напредних микро уређаја, породица ГАЛ компаније Пхилипс Семицондуцторс, КСЦ7300 и ЕПЛД компаније КСИЛИНКС.

ФПГА производи: Серије КСЦ2000, КСЦ3000, КСЦ4000, КСЦ5000 компаније КСИЛИНКС, пАСИЦ1 КуицкЛогиц-а, МАКС5000 компаније Алтера.

Примене АСИЦ-а

Јединственост АСИЦ-а револуционирала је начин производње електронике. То је смањило величину матрице истовремено повећавајући густину логичка врата по чипу. АСИЦ-и су обично преферирани за апликације високог нивоа. АСИЦ чип се користи као ИП језгра за сателите, производњу РОМ-а, Микроконтролер и разне врсте примена у медицинском и истраживачком сектору. Једна од трендовских примена АСИЦ-а је БИТЦОИН МИНЕР.

Битцоин Минер

Рударство криптовалута захтева већу снагу и брзи хардвер. ЦПУ опште намене не може да обезбеди тако већи рачунски капацитет великом брзином. АСИЦ рудари биткоина су чипови уграђени у посебно дизајниране матичне плоче и напајања , конструисани у једну целину. То је наменски дизајниран хардвер до нивоа чипа за рударство биткоина. Ове јединице могу извршавати алгоритам само једне крипто валуте. За другу врсту крипто валуте, претпоставља се, потребан нам је други рудар.

Предности и недостаци АСИЦ-а

Тхе предности АСИЦ-а укључи следеће.

- Мала величина АСИЦ-а чини га великим избором за софистициране веће системе.

- Како је велики број кола изграђених преко једног чипа, то узрокује велике брзине апликација.

- АСИЦ има малу потрошњу енергије.

- Како су систем на чипу, кругови су присутни један поред другог. Дакле, за повезивање различитих кола потребно је врло минимално усмеравање.

- АСИЦ нема проблема са временом и конфигурацијом постпродукције.

Тхе недостаци АСИЦ-а укључи следеће.

- Како се ради о прилагођеним чиповима, они пружају малу флексибилност за програмирање.

- Будући да ови чипови морају бити дизајнирани од основног нивоа, они имају високу цену по јединици.

- АСИЦ има веће време за пласирање на тржиште.

АСИЦ вс ФПГА

Разлика између АСИЦ и ФПГА укључује следеће.

АСИЦ | ФПГА |

| Није могуће програмирати | Препрограмибилно |

| Преферира се за велике обимне продукције | Преферира се за продукције мале количине |

| То су специфични за примену | Користи се као прототипови система |

| Енергетски ефикасан захтева мање снаге | Мање енергетски ефикасно захтева више снаге |

| То су трајна кола која се не могу с времена на време надоградити. | Изузетно погодан за апликације у којима се коло мора с времена на време надоградити, као што су чипови мобилних телефона, базне станице итд |

Дакле, овде се ради о прегледу Интегрисани круг специфичан за апликацију . Изум АСИЦ-а изазвао је огромну промену у начину на који се користи електроника. АСИЦ користимо у свакодневном животу у облику различитих апликација. На које апликације АСИЦ-а сте наишли? Са којом врстом АСИЦ-а сте радили?